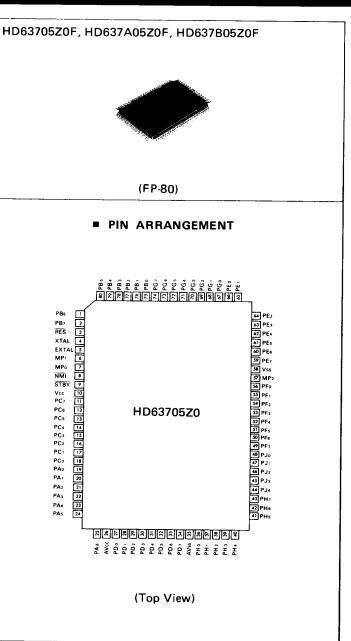

## HD63705Z0, HD637A05Z0, HD637B05Z0 ZTAT<sup>™</sup> Micro

Preliminary AUGUST, 1986

#U170

# HITACHI

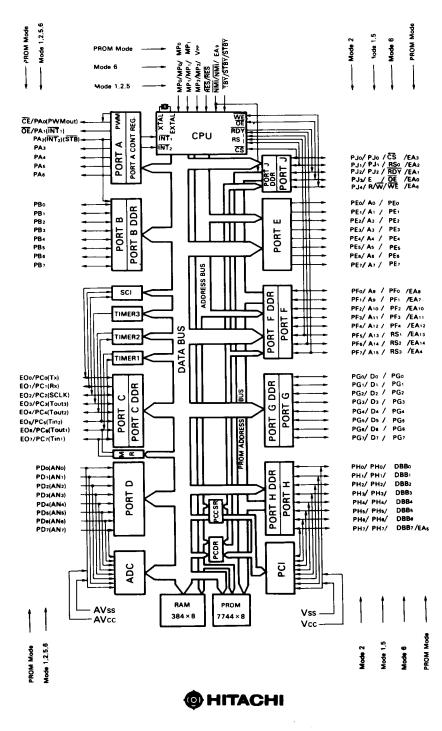

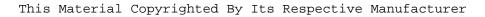

The HD63705Z0 is an 8-bit high performance CMOS single chip microcomputer unit (MCU) which includes 8k bytes of PROM and is object code compatible with the HD6305 Family.

This MCU contains a CPU, 8k bytes of PROM, 384 bytes of RAM, 8-channel A/D converter, five 16-bit timers, PWM timer, serial communication interface (SCI) and 68 parallel I/O pins.

Moreover, the HD63705Z0 provides a slave processor mode which allows to this MCU to operate as an intelligent peripheral interface adapter LSI.

#### FEATURES

#### <Hardware Features>

- 7744 bytes of PROM (Compatible with 27256 type)

- 384 bytes of RAM

- 8-bits X 8-channel A/D converter

- Five 16-bit timers

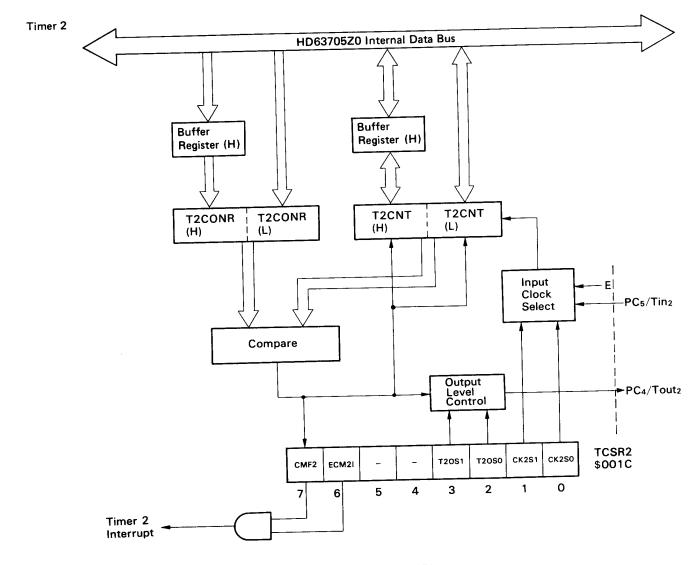

- 16-bit Reloadable Counter X 2 ..... Timer 2

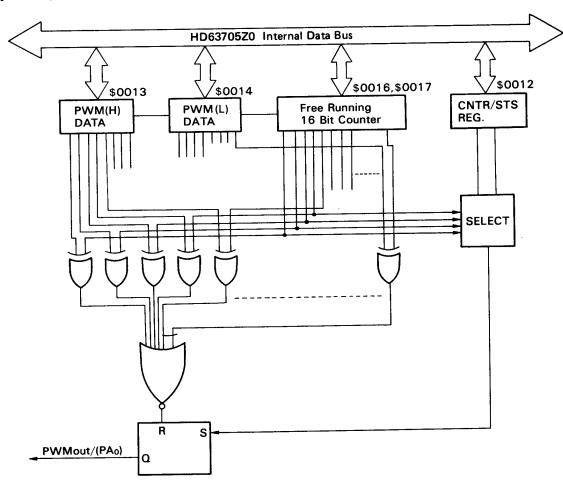

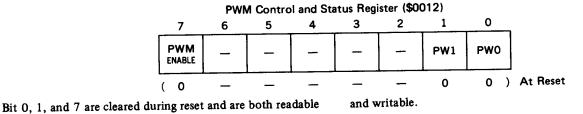

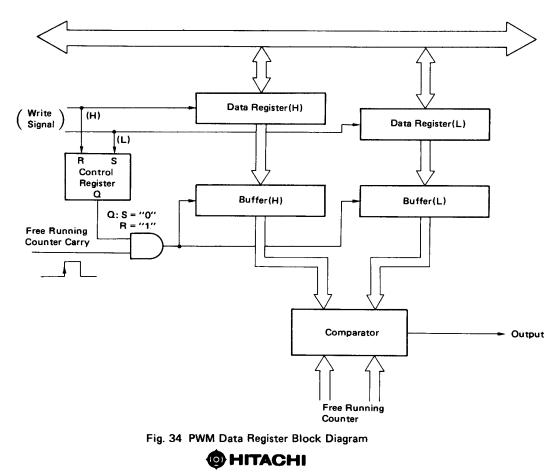

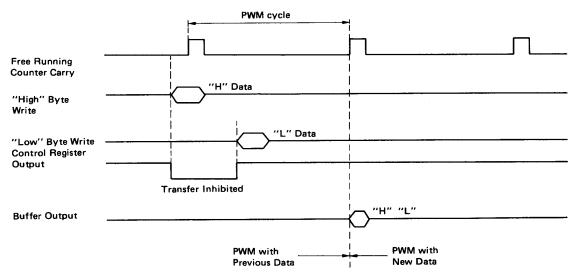

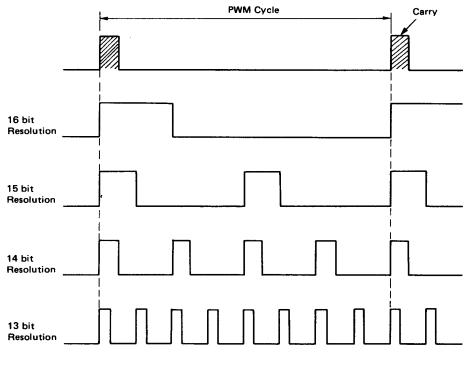

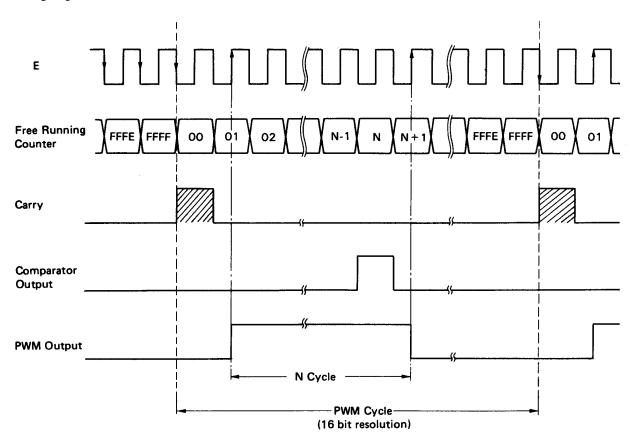

- PWM (Pulse Width Modulation) timer

- Cycle: 2<sup>13</sup> to 2<sup>16</sup> cyc. (software programmable) On-chip serial communication interface (SCI)

- Asynchronous mode (8 kinds of data formats, hardware parity)

- Synchronous mode

- 68 parallel I/O pins (in single chip mode) 45 I/O pin (including eight input data latch ports) 15 output pins

- 8 input pins

- Internal power-on reset circuit

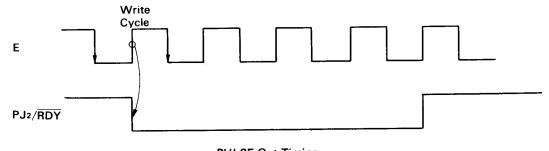

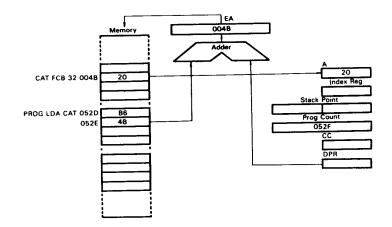

- Direct Page Register which allows for powerful page manipulation

- A variety of external interrupts Three external, three timer, one parallel, one serial, one A/D and one software interrupts provided.

- A variety of operating modes

- MCU mode

(Mode 2)

Master MCU single chip mode

(Mode 2)

Slave MCU single chip mode

(Mode 6)

Master MCU external extended mode

(Mode 1)

(Internal ROM is enabled.)

(Mode 5)

(Internal ROM is disabled.)

(Mode 4)

- Max. 65k bytes of address locations

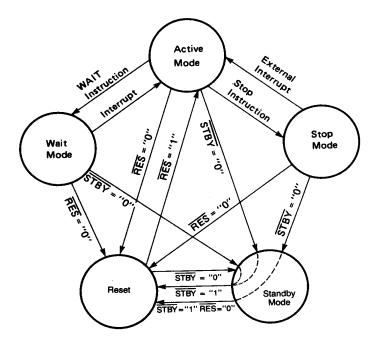

- Low power modes

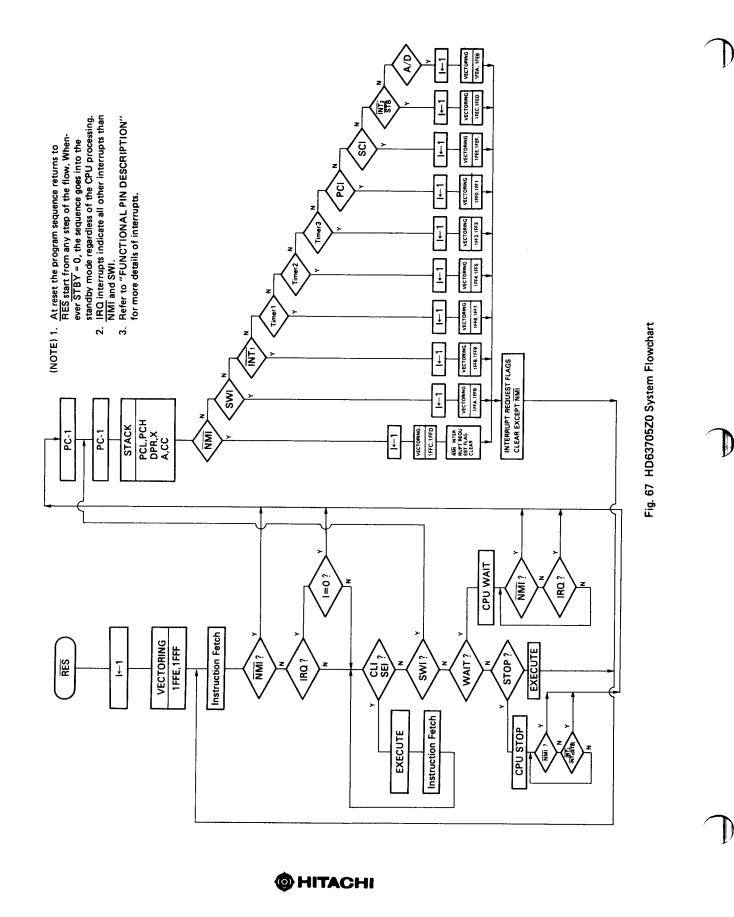

- Wait mode . . . . Internal oscillator remains active. The CPU processing is halted. The timer, serial, parallel, A/D and external interrupts are enabled.

- Stop mode . . . . . Internal oscillator is halted. The data of registers and RAM remain unaltered. All I/O lines remain unchanged. External interrupts are enabled.

- Standby mode . . Internal oscillator is halted. The data of RAM is unchanged. The MCU internal state is reset.

- Minimum instruction cycle time . . . . 0.5 μs (f = 2 MHz)

- Operating range

- $V_{CC} = 5V \pm 10\% \quad f = 0.1 \text{ to } 1.0 \text{ MHz} : \text{HD63705Z0} \\ f = 0.1 \text{ to } 1.5 \text{ MHz} : \text{HD637A05Z0} \\ f = 0.1 \text{ to } 2.0 \text{ MHz} : \text{HD637B05Z0}$

- BLOCK DIAGRAM

2

#### <Software Features>

- Upward software compatible with the HD6305 family MCUs (Multiply instruction (MUL) is added.)

- Byte efficient instruction set

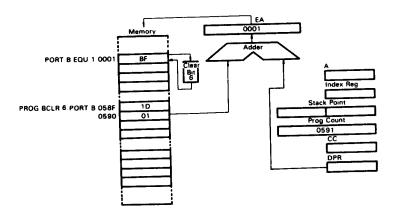

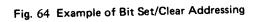

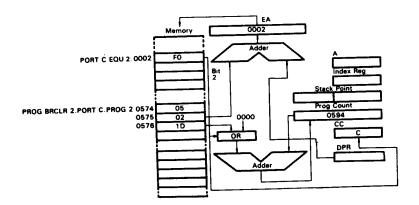

- Powerful bit manipulation instructions

- Bit test and branch instructions

- Versatile interrupt handling

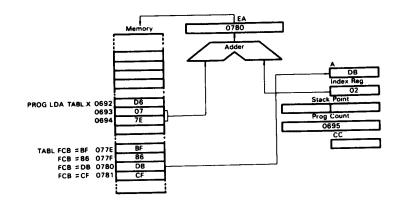

- Powerful indexed addressing for tables

- Full set of conditional branches

- 10 powerful addressing modes

#### ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol                             | Value                    | Unit | Note |

|-----------------------|------------------------------------|--------------------------|------|------|

| Supply Voltage        | V <sub>CC</sub> , AV <sub>CC</sub> | -0.3 ~ + 7.0             | v    |      |

| Programming Voltage   | VPP                                | 0.3 ~ + 15.0             | v    | 1    |

| Input Voltage         | V <sub>in</sub>                    | $-0.3 \sim V_{CC} + 0.3$ | V    | 2    |

| Operating Temperature | T <sub>op r</sub>                  | 0~+70                    | °C   |      |

| Storage Temperature   | T <sub>stg</sub>                   | -55~+125                 | °C   |      |

(NOTE 1) Applies to MP<sub>2</sub> (V<sub>PP</sub>) pin.

(NOTE 2) Applies to all other pins except for  $MP_2$  (V<sub>PP</sub>).

These devices contain circuits to protect the inputs against high static voltages or high electric fields. Be careful not to apply any voltage higher than the absolute maximum ratings to these high input impedance circuits. For normal operation, we recommend the Vin and Vout be constrained to the range  $V_{SS} \leq (Vin \text{ or Vout}) \leq V_{CC}$ .

#### ELECTRICAL CHARACTERISTICS IN MCU MODE

### • D.C. Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND, T<sub>a</sub> = 0 to +70°C, unless otherwise noted.

| <u></u>                        | ltem                                                                  | Symbol           | Test Condition                                   | min                   | typ | max                   | Unit |

|--------------------------------|-----------------------------------------------------------------------|------------------|--------------------------------------------------|-----------------------|-----|-----------------------|------|

|                                | RES, STBY,                                                            |                  |                                                  | V <sub>CC</sub> - 0.5 |     | V <sub>CC</sub> + 0.3 |      |

|                                | EXTAL                                                                 |                  |                                                  | $V_{CC} \times 0.7$   | -   | $V_{CC} + 0.3$        |      |

|                                | Port D                                                                |                  |                                                  | 2.0                   |     | $AV_{CC} + 0.3$       | _    |

| Input High Voltage             | SCLK, INT2 (STB)                                                      | V <sub>IH</sub>  |                                                  | $V_{CC} \times 0.8$   | —   | $V_{\rm CC}$ + 0.3    | V    |

|                                | PCI Inputs****                                                        |                  |                                                  | 2.4                   | -   | $V_{cc} + 0.3$        |      |

|                                | All Other Inputs                                                      |                  |                                                  | 2.0                   | -   | $v_{CC} + 0.3$        |      |

|                                | PCI Inputs * * * *                                                    |                  |                                                  | -0.3                  | -   | 0.6                   | - v  |

| Input Low Voltage              | All Other Inputs                                                      | VIL              |                                                  | -0.3                  |     | 0.8                   | ] `  |

| <u> </u>                       | NMI, RES, STBY                                                        |                  |                                                  |                       | -   | 1.0                   |      |

| Input Leakage Current          | MP <sub>2</sub> (V <sub>PP</sub> )                                    | I <sub>in</sub>  | $V_{in} = 0.5$ to $V_{CC} - 0.5V$                | -                     | 1.0 | 100                   | μΑ   |

| Three State<br>Leakage Current | Ports A*, B, C, G, E**,<br>F, H, J, MP <sub>0</sub> , MP <sub>1</sub> | I <sub>TS1</sub> | $V_{in} = 0.5 \text{ to } V_{CC} - 0.5 \text{V}$ | _                     | -   | 1.0                   |      |

|                                |                                                                       |                  | I <sub>OH</sub> = -200 μA                        | 2.4                   | —   |                       | V    |

| Output High Voltage            | All Outputs but PJ <sub>2</sub>                                       | V <sub>он</sub>  | $I_{OH} = -10 \mu A$                             | V <sub>CC</sub> - 0.7 | -   | _                     | V    |

|                                | All Outputs Including PJ2****                                         |                  | I <sub>OL</sub> = 1.6 mA                         | — .                   | -   | 0.4                   | V    |

| Output Low Voltage             | Port E                                                                | V <sub>OL</sub>  | $I_{OL} = 10 \text{ mA}$                         | _                     |     | 1.0                   | V _  |

| Input Capacitance              | MP <sub>2</sub> (V <sub>PP</sub> )                                    | C <sub>in</sub>  | 14 014 ( ANUL T 050C                             | —                     | -   | 100                   | pF   |

| Input Capacitance              | All Other Except for MP <sub>2</sub> (V <sub>PP</sub> )               | - <sup>-</sup> " | $V_{in} = 0V, f = 1MHz, T_a = 25^{\circ}C$       | _                     | -   | 12.5                  |      |

|                                | Active                                                                | Icc***           |                                                  | _                     | 6   | 12                    | mA   |

|                                | Wait                                                                  | WAIT***          | 1                                                | -                     | 2   | 5                     | mA   |

| Current Dissipation * *        | Stop                                                                  | ISTOP            | f = 1MHz***                                      |                       | 3.0 | 15.0                  | μA   |

|                                | Standby                                                               | ISTBY            | 1                                                | -                     | 3.0 | 15.0                  | μA   |

| RAM Standby Voltage            |                                                                       | VRAM             | ······································           | 2.0                   | -   | -                     | V    |

\* Only in the standby mode.

\*\* V<sub>IH</sub> min = V<sub>CC</sub> - 1.0V, V<sub>IL</sub> max. = 0.8V and no line is connected to any output or  $\overline{\text{RES}}$  pin.

\*\*\* The value at f = XMHz is given by  $I_{CC}$  (f = XMHz) =  $I_{CC}$  (f = 1MHz, XX.

\*\*\*\* PJ2 is an NMOS open drain pin.

\*\*\*\*\* RSO ~ 3, DBBO ~ 7, CS, OE WE.

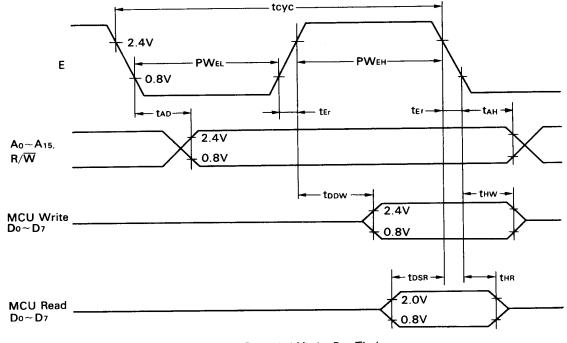

### • AC Characteristics (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND, Ta = 0 to +70°C, unless otherwise noted)

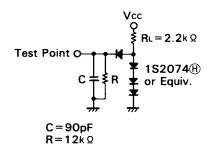

#### **Bus Timing**

| Item                             | Symbol           | Test      | на  | 063705 | Z0  | HD    | 537A05 | 5Z0 | нр  | 637B0 | 5Z0 | Unit |

|----------------------------------|------------------|-----------|-----|--------|-----|-------|--------|-----|-----|-------|-----|------|

|                                  |                  | Condition | min | typ    | max | min   | typ    | max | min | typ   | max | Onit |

| Cycle Time                       | t <sub>cyc</sub> |           | 1.0 | -      | 10  | 0.666 | _      | 10  | 0.5 | _     | 10  | μs   |

| System Clock Rise Time           | t <sub>Er</sub>  |           | _   | _      | 25  | -     |        | 25  | _   |       | 25  | ns   |

| System Clock Fall Time           | tEf              |           | _   | _      | 25  | _     |        | 25  |     | _     | 25  | ns   |

| System Clock Pulse Width (High)* | PWEH             |           | 450 | _      | -   | 300   | _      | _   | 220 | _     | _   | ns   |

| System Clock Pulse Width (Low)*  | PWEL             | Fig. 1    | 450 |        | _   | 300   | -      | -   | 220 | _     | _   | ns   |

| Address, R/W Delay Time*         | t <sub>AD</sub>  |           | _   | _      | 250 | _     |        | 190 | _   | _     | 160 | ns   |

| Data Delay Time (Write)          | tDDW             |           | _   | -      | 200 | _     |        | 160 | _   | _     | 120 | ns   |

| Data Setup Time (Read)           | t <sub>DSR</sub> |           | 80  | _      | _   | 70    | _      | _   | 70  |       | _   | ns   |

| Address, R/W Hold Time*          | t <sub>AH</sub>  |           | 40  | _      | -   | 30    | _      |     | 20  |       | _   | ns   |

| Data Hold Time (Write)*          | t <sub>HW</sub>  | ľ         | 40  | _      | _   | 30    |        |     | 20  | _     | _   | ns   |

| Data Hold Time (Read)            | t <sub>HR</sub>  |           | 0   | -      |     | 0     | _      | _   | 0   | _     | -   | ns   |

\* Bus timing varies with  $t_{CYC}$ . The above characteristics are obtained when  $t_{CYC}$  is a minimum (i.e. during highest speed operation).

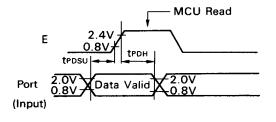

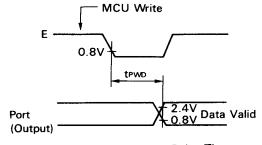

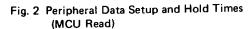

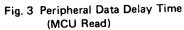

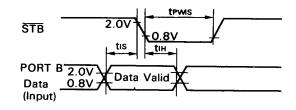

#### **Peripheral Port Timing**

| lte                           | m                             | Symbol            | Test      | HD63705Z0 |     | HD637A05Z0 |     |     | HD637B05Z0 |     |     | Unit |     |

|-------------------------------|-------------------------------|-------------------|-----------|-----------|-----|------------|-----|-----|------------|-----|-----|------|-----|

|                               |                               |                   | Condition | min       | typ | max        | min | typ | max        | min | typ | max  | Omt |

| Peripheral Data<br>Setup Time | Port B, C, D,<br>F, G, H, J   | <sup>t</sup> pdsu | 5:- 0     | 200       | -   | -          | 200 | -   | -          | 200 | _   | _    | ns  |

| Peripheral Data<br>Hold Time  | Port B, C, D<br>F, G, H, J    | <sup>t</sup> PDH  | Fig. 2    | 200       |     | _          | 200 | _   | _          | 200 | -   | -    | ns  |

| Delay Time                    | Port A, B, C<br>E, F, G, H, J | tpwd              | Fig. 3    | -         | -   | 300        |     | -   | 300        |     | _   | 300  | ns  |

| Input Strobe Pul              | se Width                      | tpwis             |           | 300       | _   |            | 300 | -   | _          | 300 | _   |      | ns  |

| Input Data<br>Hold Time       | Port B                        | t <sub>IH</sub>   | Fig. 4    | 200       | -   | _          | 200 |     | _          | 200 | _   | -    | ns  |

| Input Data<br>Setup Time      | Port B                        | t <sub>IS</sub>   |           | 100       | _   | _          | 100 | -   | _          | 100 | -   | _    | ns  |

\* Enable negative transition to peripheral data valid.

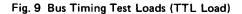

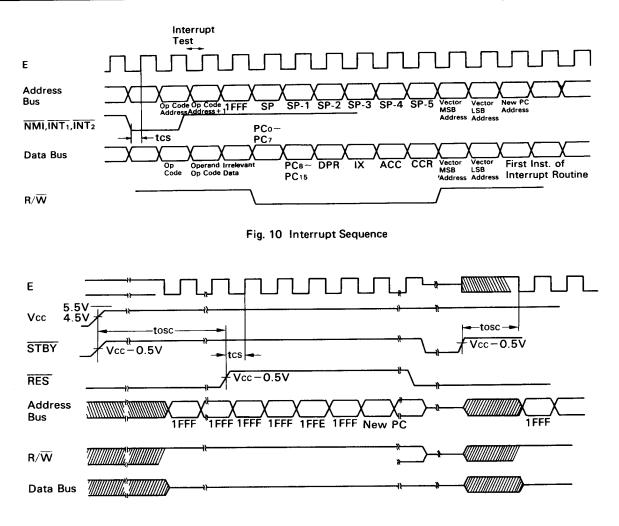

### • Control Signal Timing (V<sub>CC</sub> = 5.0V $\pm$ 10%, V<sub>SS</sub> = GND, Ta = 0 to +70°C unless otherwise noted)

| Item                                                      | Symbol            | Test        | н                                   | D6370 | 5Z0 | н                        | D637 A | )5Z0 | HD637B05Z0               |     |     | Unit             |

|-----------------------------------------------------------|-------------------|-------------|-------------------------------------|-------|-----|--------------------------|--------|------|--------------------------|-----|-----|------------------|

|                                                           |                   | Condition   | min                                 | typ   | max | min                      | typ    | max  | min                      | typ | max | Unit             |

| NMI Pulse Width                                           | tiwL              |             | t <sub>cyc</sub><br>+250            | _     | -   | t <sub>cyc</sub><br>+200 | —      | -    | t <sub>сус</sub><br>+200 | —   | -   | ns               |

| $\overline{INT}_1$ , $\overline{INT}_2$ (STB) Pulse Width | T <sub>IWL2</sub> |             | <sup>t</sup> <sub>сус</sub><br>+250 | -     | _   | t <sub>cyc</sub><br>+200 | _      | _    | <sup>t</sup> сус<br>+200 | _   | -   | ns               |

| RES Pulse Width                                           | trwl              |             | 5                                   | -     |     | 5                        | _      | -    | 5                        |     | -   | t <sub>cyc</sub> |

| Control Setup Time                                        | t <sub>CS</sub>   | Fig. 10, 11 | 250                                 | -     | _   | 250                      | -      | _    | 250                      | -   | -   | ns               |

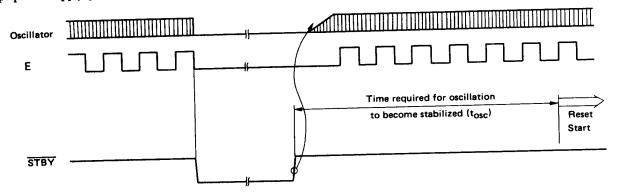

| Oscillation Start Time (Crystal)                          | tosc              | Fig. 11*    | —                                   | -     | 20  | -                        | _      | 20   | -                        | -   | 20  | ms               |

| Reset Delay Time                                          | t <sub>RHL</sub>  | **          | 80                                  | -     | -   | 80                       | -      | _    | 80                       | -   |     | ms               |

\*  $C_L = 22 \text{ pF} \pm 20\%$ ,  $R_S = 60\Omega \text{ max}$ .

\*\* External capacitance is 2.2  $\mu$ F.

4

**HITACHI**

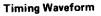

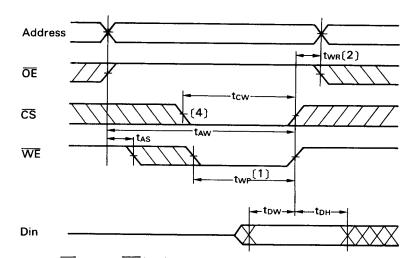

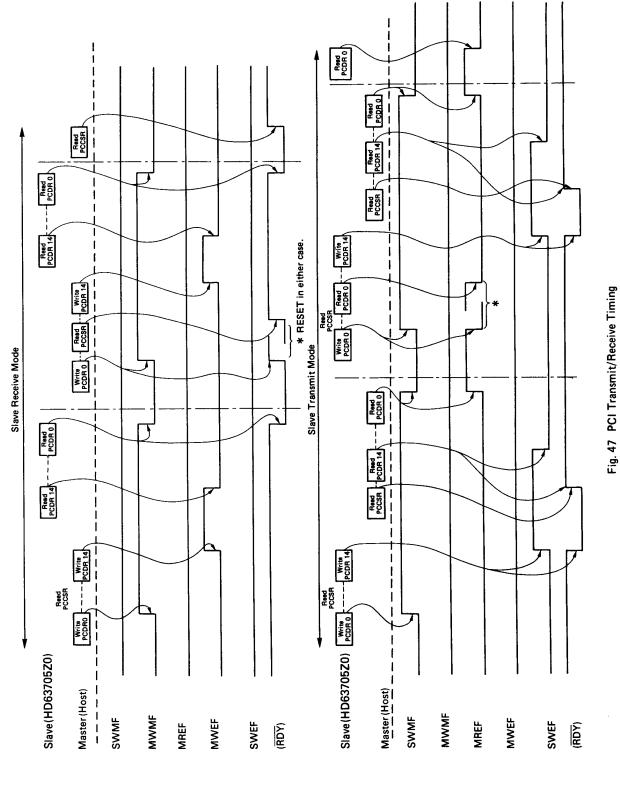

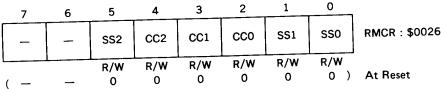

#### PCI Timing

#### Read Cycle

|                                 |                  | HD63705Z0 |     | HD637A05Z0 |     | HD637 | 7B05Z0 | Unit |

|---------------------------------|------------------|-----------|-----|------------|-----|-------|--------|------|

| Item                            | Symbol           | min       | max | min        | max | min   | max    |      |

| Address Access Time             | t <sub>AA</sub>  |           | 300 | _          | 250 | —     | 200    | ns   |

| Chip Select Access Time         | t <sub>ACS</sub> | T         | 300 |            | 250 | -     | 200    | ns   |

| Output Enable Output Delay Time | t <sub>OE</sub>  | <u> </u>  | 150 |            | 120 | -     | 110    | ns   |

| CS Output Floating              | t <sub>CHZ</sub> | -         | 150 | -          | 120 |       | 110    | ns   |

| Output Hold Time                | t <sub>OH</sub>  | 0         | _   | 0          | -   | 0     | -      | ns   |

| OE Output Floating              | t <sub>OHZ</sub> | 0         | 150 | 0          | 120 | 0     | 110    | ns   |

#### Write Cycle

|                      | Symbol          | HD63 | 705Z0 | HD637A05Z0 |     | HD637 | B05Z0 | Unit |

|----------------------|-----------------|------|-------|------------|-----|-------|-------|------|

| ltem                 |                 | min  | max   | min        | max | min   | max   |      |

| Chip Select Time     | tcw             | 200  | -     | 150        | -   | 120   | -     | ns   |

| Address Valid Time   | t <sub>AW</sub> | 200  | _     | 150        | -   | 120   | -     | ns   |

| Address Setup Time   | t <sub>AS</sub> | 20   | -     | 20         | -   | 20    | 1     | ns   |

| Write Pulse Width    | twp             | 150  | _     | 120        | _   | 100   | -     | ns   |

| Address Hold Time    | twn             | 20   | -     | 20         | -   | 20    | -     | ns   |

| Input Data Set Time  | t <sub>DW</sub> | 120  | -     | 100        | _   | 80    |       | ns   |

| Input Data Hold Time | <sup>t</sup> DH | 20   | -     | 20         | -   | 20    | _     | ns   |

Write Cycle\*1

(NOTES) 1. A write occurs during the overlap of a low CS and a low WE (twp).

2. twn is measured from the earlier of CS or WE going high to the end of write cycle.

If I/O pins are in the output state, input signal with opposite phase to the outputs must not be applied to them.

If the CS negative transition occurs simultaneously with the WE negative transition, the output remains in a high impedance state.

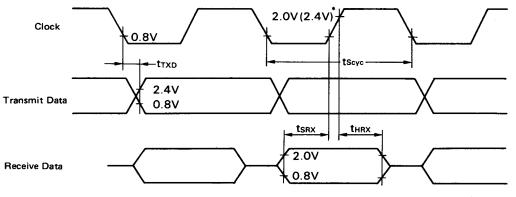

#### **Timer and SCI Timing** •

|                                                   | ltem                           | Symbol             | Test      | H   | 063705 | Z0  | HD  | 637A05 | 5Z0 | нс  | 637B0 | 5Z0 | Unit             |

|---------------------------------------------------|--------------------------------|--------------------|-----------|-----|--------|-----|-----|--------|-----|-----|-------|-----|------------------|

|                                                   |                                |                    | Condition | min | typ    | max | min | typ    | max | min | typ   | max |                  |

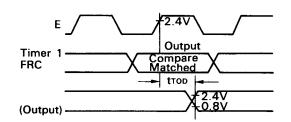

| •                                                 | ut Pulse Width                 | tpwt               | Fig. 8    | 2.0 | _      | -   | 2.0 |        | _   | 2.0 | _     | _   | t <sub>cyc</sub> |

| Delay Time (<br>Transition to<br>Valid)           | (Enable Positive<br>Timer Data | t <sub>TOD</sub>   | Fig. 6, 7 | _   | -      | 400 | _   | -      | 400 | _   | _     | 400 | ns               |

| SCI Input                                         | Asynchronous<br>Mode           |                    | Fig. 8    | 1.0 | -      | -   | 1.0 | _      | _   | 1.0 | _     | -   | t <sub>cyc</sub> |

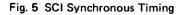

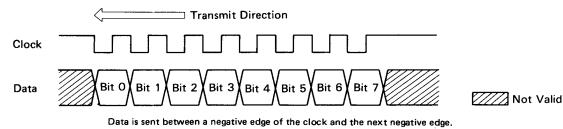

| Clock Cycle                                       | Synchronous<br>Mode            | t <sub>Scyc</sub>  | Fig. 5    | 2.0 | _      | -   | 2.0 | _      | -   | 2.0 | -     | -   | t <sub>cyc</sub> |

| SCI Transmit<br>Delay Time<br>(Synchronou         |                                | <sup>t</sup> txd   |           | _   | -      | 200 | _   | _      | 200 | -   | _     | 200 | ns               |

| SCI Receive I<br>(Synchronou                      | Data Setup Time<br>s Mode)     | tsrx               | Fig. 5    | 260 | -      | -   | 260 | -      | -   | 260 |       | _   | ns               |

| SCI Receive I<br>(Synchronou                      | Data Hold Time<br>s Mode)      | <sup>t</sup> нях   |           | 100 | -      |     | 100 | -      | —   | 100 | -     |     | ns               |

|                                                   | ock Pulse Width                | <sup>t</sup> PWSCK | Fig. 8    | 0.4 |        | 0.6 | 0.4 |        | 0.6 | 0.4 |       | 0.6 | tScyc            |

| Timer 2 Inpu                                      | t Clock Cycle                  | t <sub>tcyc</sub>  | Fig. 8    | 2.0 | -      | _   | 2.0 | _      | -   | 2.0 |       |     | t <sub>cyc</sub> |

| Timer 2 Inpu<br>Width                             | t Clock Pulse                  | <sup>t</sup> рwтск |           | 200 | -      | _   | 200 | _      | _   | 200 | _     | _   | ns               |

| Timer 1, Timer 2 and SCI<br>Input Clock Rise Time |                                | t <sub>CKr</sub>   | Fig. 8    | _   | -      | 100 | _   |        | 100 | -   | -     | 100 | ns               |

| Timer 1, Timer 2 and SCI<br>nput Clock Fall Time  |                                | <sup>t</sup> CKf   |           | -   | -      | 100 | _   | -      | 100 | -   | _     | 100 | ns               |

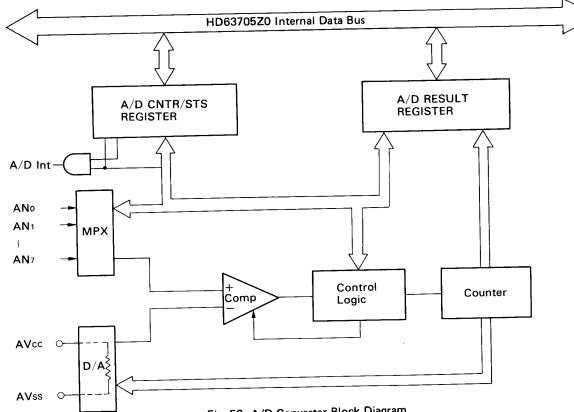

A/D Converter Characteristics (V<sub>CC</sub> = 5.0 ± 10%, V<sub>SS</sub> = AV<sub>SS</sub> = GND, Ta = 0 to +70°C, unless otherwise noted)

| ltem                                  | Symbol | Test       | HD63705Z0 |     |      | HD637A05Z0       |     |      | HD637B05Z0 |     |      | Unit    |

|---------------------------------------|--------|------------|-----------|-----|------|------------------|-----|------|------------|-----|------|---------|

|                                       | -,     | Condition  | min       | typ | max  | min              | typ | max  | min        | typ | max  | Unit    |

| Analog Power Supply Voltage           | AVcc   |            | 4.5       | _   | 5.5  | 4.5              | _   | 5.5  | 4.5        |     | 5.5  | v       |

| Analog Input Voltage                  | AVin   | 1          | AVSS      | _   | AVcc | AV <sub>SS</sub> |     | AVcc | AVSS       |     | AVcc | V       |

| Current between                       | IAD    | Operation  |           |     | 1.0  |                  |     | 1.0  |            |     | 1.0  | mA      |

| AV <sub>CC</sub> and AV <sub>SS</sub> | - 40   | STBY, STOP |           |     | 250  |                  |     | 250  |            |     | 250  | μA      |

| Resolution                            |        |            | -         | 8   |      | -                | 8   | _    | -          | 8   | -    | bit     |

| Conversion Time                       |        |            | 34        | _   | _    | 34               |     | -    | 34         |     | _    | μs      |

| Input Count                           |        |            | 0         | _   | 8    | 0                |     | 8    | 0          | _   | 8    | Channel |

| Absolute Error                        |        | Ta=25°C    | -         | -   | 1.5  | -                | _   | 1.5  | _          | _   | 1.5  | LSB     |

(NOTE) AV<sub>CC</sub> = V<sub>CC</sub>  $\pm$  0.3V

**OHITACHI**

Fig. 1 External Extended Modes Bus Timing

Fig. 4 Port B Input Latch Timing

\* 2.0V is high level when clock input. 2.4V is high level when clock output.

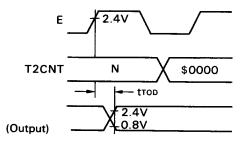

Fig. 6 Timer 1 Output Timing

8

(TCONR = N)

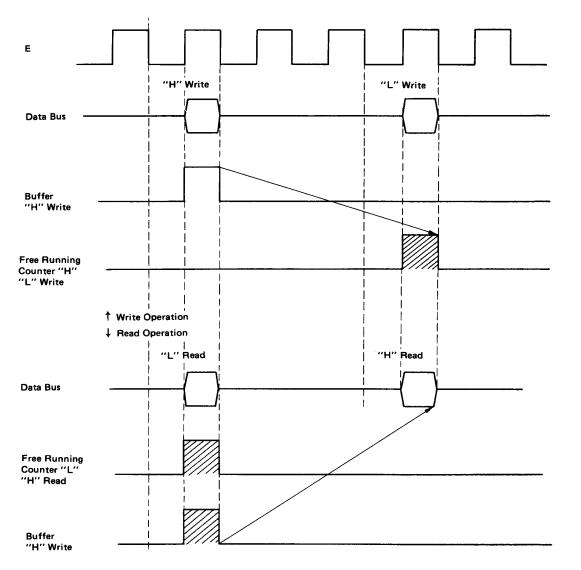

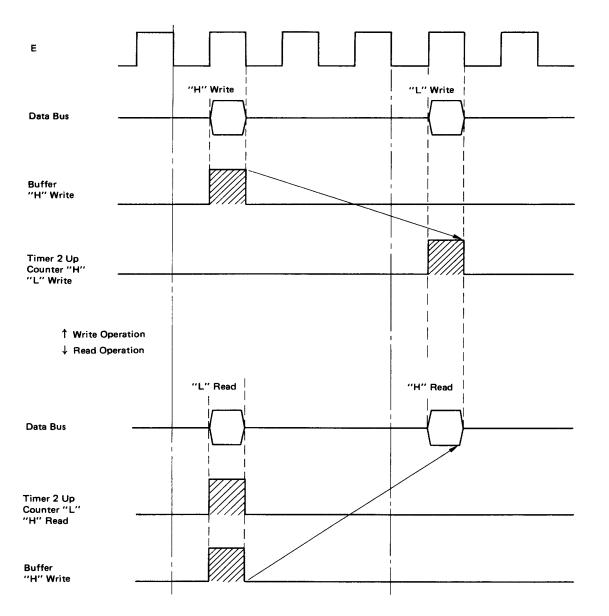

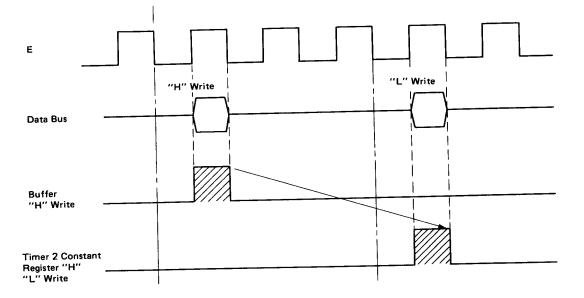

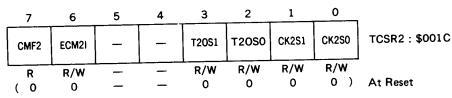

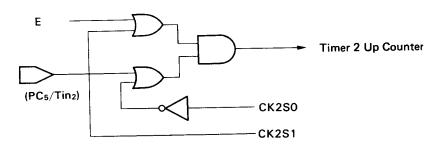

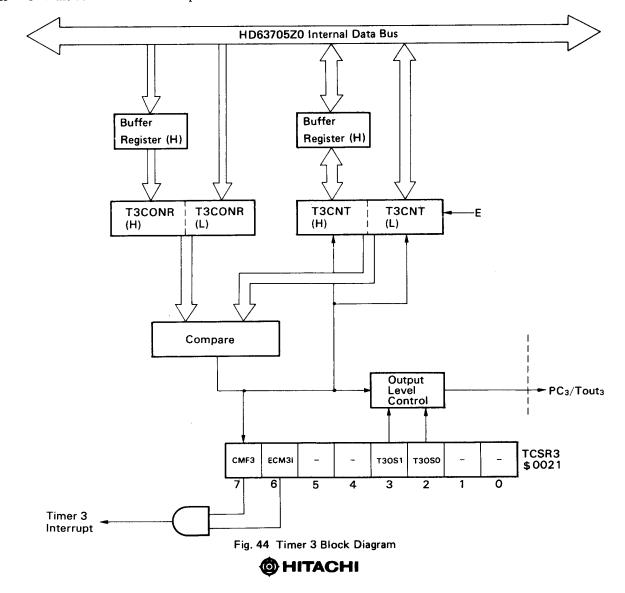

Fig. 7 Timer 2 and Timer 3 Output Timing

**O HITACHI**

Fig. 11 Reset Timing

#### FUNCTIONAL PIN DESCRIPTION

Of the 80 MCU pins, some function depending on the operating modes. For details, see Table 1.

#### Mode Independent Pins

The following pins function identically in all modes.

#### • V<sub>CC</sub>, V<sub>SS</sub>

Power is supplied to a large portion of the MCU using the  $V_{CC}$  and  $V_{SS}$  pins. The power supply should provide +5V±10% for  $V_{CC}$ .

#### AV<sub>CC</sub>, AV<sub>SS</sub>

These are power supply pins for A/D converter, which can be used separately from  $V_{SS}$  and  $V_{CC}$  to enhance the precision of A/D conversion.

#### XTAL, EXTAL

These two input pins are connected to an AT-cut parallel crystal resonator to drive the MCU internal oscillator. Dividedby-four circuitry is included which allows use of the 4 MHz crystal resonator for obtaining a system clock of 1 MHz.

Alternatively, EXTAL can be driven by an external clock with a duty cycle of 45 to 55% with no line connected to

XTAL, when a system clock with a fourth frequency of the external clock is generated. The external clock frequency should be less than four times of the maximum operating frequency.

#### • STBY

This pin is used to put the MCU in the standby mode or PROM programming mode.

Logic low on the STBY pin allows the MCU to enter the standby mode. In this mode the internal oscillator is turned off, the internal clock is halted, and the MCU internal state is reset. Writing a 0 to the RAM enable bit (RAME) disables RAM, which allows data in the RAM to be unchanged in the standby mode. RAME is bit 4 of the Miscellaneous Register at \$003B. For detailed information about the standby mode, see 'LOW POWER MODES'.

When applying logic lows to the  $\overline{\text{STBY}}$  pin and mode programming pins MP<sub>0</sub> and MP<sub>1</sub> and applying a logic high to MP<sub>2</sub>, the MCU enters the PROM programming mode. For details, see 'PROGRAMMING THE PROM'.

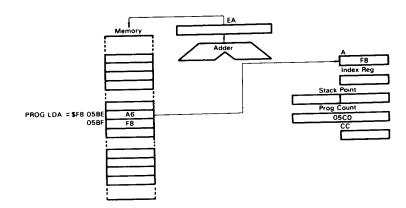

#### RESET (RES)

The  $\overline{RES}$  pin is used to reset the MCU to provide a startup from a power down condition. On power-up, the  $\overline{RES}$  must stay low for minimum of 20 ms.

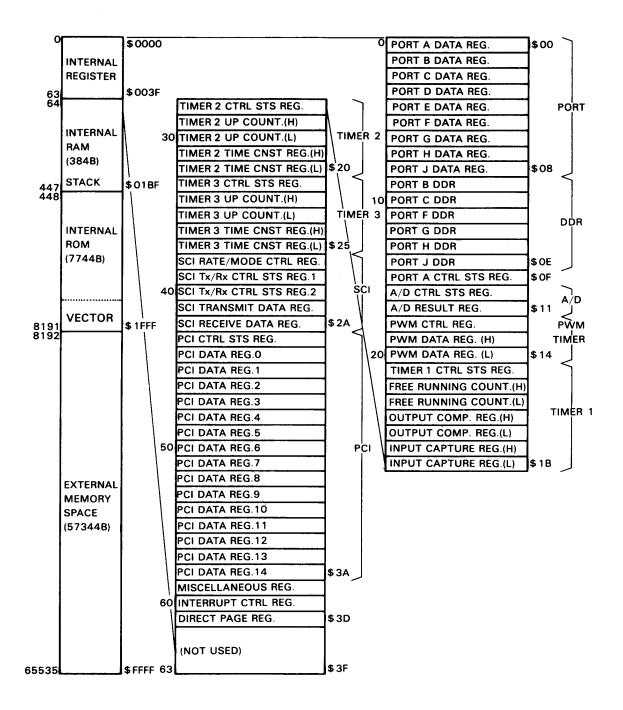

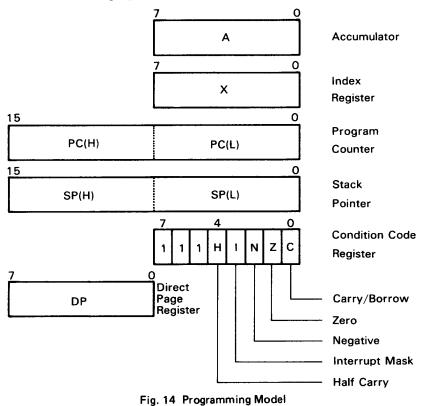

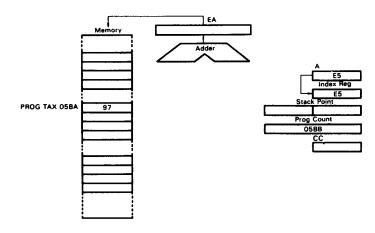

As the CPU registers (Accumulator, Index Register, Stack Pointer, Condition Code Register except for interrupt mask bit), RAM, port data registers are not initialized at reset, their contents are indeterminate after the startup procedure. To reset the MCU during the operation, the RES should be held low for at least five system clock cycles. At the fifth cycle, all address buses go high.

The address buses remain high as long as the  $\overline{RES}$  stays low. When applying a logic high to the  $\overline{RES}$ , the MCU operates as follows:

- 1) Latches the data on the mode programming pins  $MP_0$ ,  $MP_1$  and  $MP_2$ . (In the PROM programming mode, the RES is not used.)

- 2) Initializes the internal registers. (See Table 7).

- 3) Sets the interrupt mask bit in the Condition Code Register. For the CPU to recognize the maskable interrupts (INT<sub>1</sub>, INT<sub>2</sub>, and Timer 1, Timer 2, Timer 3, PCI, SCI and A/D interrupts), this bit must be cleared previously.

- 4) Puts the contents of reset vector addresses (\$1FFE, \$1FFF) into the program counter, then resumes the program execution.

After power up to the oscillator stabilization (for 20 ms max.),  $\overline{RES}$  input is not latched to the MCU, which causes the MCU internal state and I/O pin condition to be undefined.

#### **MCU Mode Pins**

The following pins function in the MCU modes (Modes 1, 2, 5, 6).

#### Non Maskable Interrupt (NMI)

An NMI negative edge signifies an interrupt request, but the current instruction will be completed before the CPU responds to the request. NMI is not affected by the interrupt mask bit in the Condition Code Register.

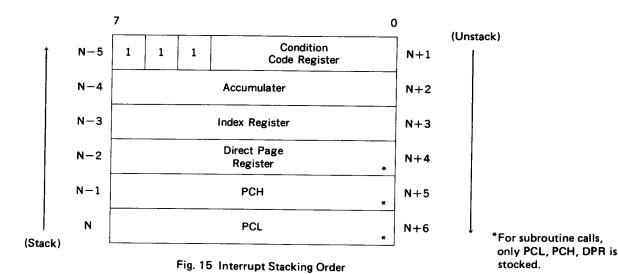

When the interrupt occurs, the contents of Program Counter, Index Register, Accumulator and Condition Code Register are pushed onto the stack. After the registers have been stacked, a vector is fetched from \$1FFC and \$1FFD, transferred to the Program Counter, then the non-maskable interrupt routine is executed.

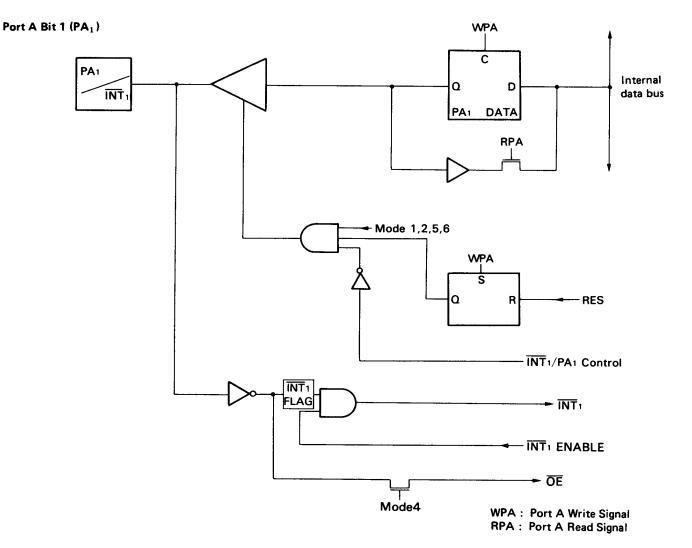

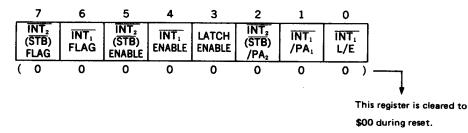

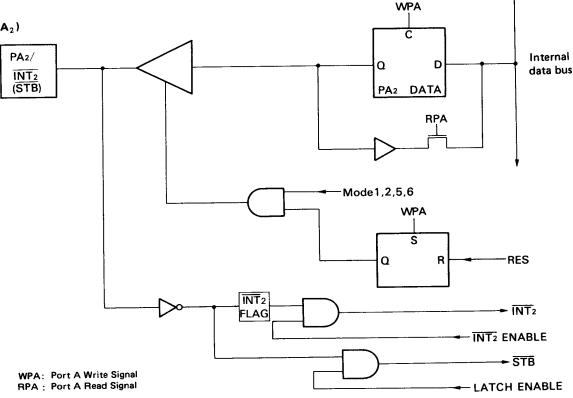

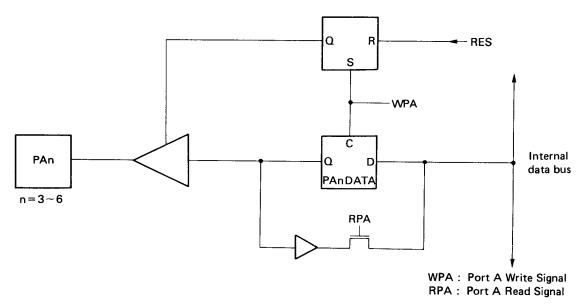

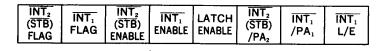

#### Interrupts (INT<sub>1</sub>, INT<sub>2</sub>)

$\overline{INT_1}$  is also used as the Port A bit 1 pin (PA<sub>1</sub>). This pin can be programmed as an  $\overline{INT_1}$  input by writing a 1 to bit 1 in the Port A Control and Status Register at \$000F.  $\overline{INT_1}$  is sensed on either a negative edge or a level of the input signal. Writing a 0 to bit 0 of the Port A Control and Status Register selects edgesensitive triggering, while writing a 1 selects level-sensitive triggering. The Port A Control and Status Register is cleared to \$00 during reset.

When  $\overline{INT_1}$  or  $\overline{INT_2}$  interrupt request is acknowledged, the CPU will complete the current instruction before it responds to the request. If the interrupt mask bit in the Condition Code Register is cleared, the CPU begins an interrupt sequence at the end of the current instruction; if set, the CPU cannot accept the interrupt request. When the interrupt occurs, the contents of Program Counter, Direct page register are pushed onto the stack, and then the interrupt mask bit is set which inhibits any additional maskable interrupts. Finally a vector is fetched, transferred to the Program Counter, and the CPU starts the interrupt service routine.

$\overline{INT_2}$  (STB) pin is also used as PA<sub>2</sub>. Writing a 1 to bit 2 in the Port A Control and Status Register allows this pin to be

10

used for the  $\overline{INT_2}$  input, and writing 1's to both bit 2 and bit 3 allows the pin to be used for STB input. After sensing the  $\overline{INT_2}$ interrupt request, the MCU processes the interrupt in the same way as the  $\overline{INT_1}$  interrupt. For details, see 'INTERRUPT'.

#### Mode Programming Pins (MP<sub>0</sub>, MP<sub>1</sub>, MP<sub>2</sub>)

These pins are used to define the HD63705Z0 operating mode. For details, see 'MODE SELECTION'.

The following pins function in the external extended modes (Mode 1 and Mode 5).

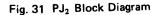

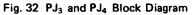

#### Enable (E: PJ<sub>3</sub>)

This pin provides the system clock for external circuits. This clock is single phase and TTL compatible. Its frequency is one fourth that of the crystal oscillator or external clock.

#### Read/Write (R/W: PJ<sub>4</sub>)

The Read/Write signal on this pin is used to control the direction of transfers on the external data bus. A low level on the R/W pin enables the data to be written to an external device. A high level on the R/W pin enables the data to be read from an external device. Normally this pin is in the read state.

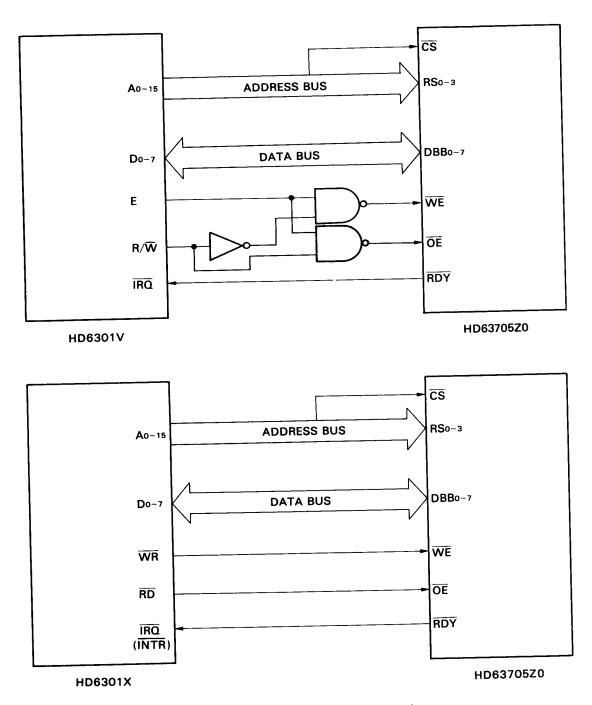

The following pins are used in the slave MCU modes (Mode 6).

#### Chip Select (CS: PJ<sub>0</sub>)

This pin allows the HD63705Z0 to provide the parallel communication with the master MCU. A low level on this pin activates the data bus.

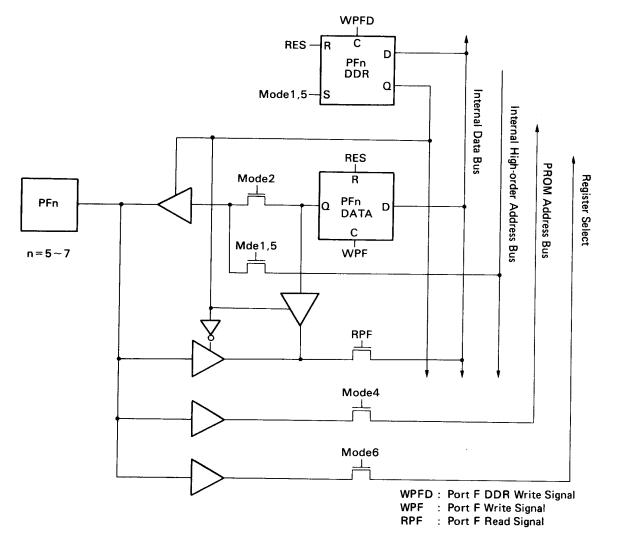

#### Register Select (RS<sub>0</sub> - RS<sub>3</sub>: PJ<sub>1</sub>, PF<sub>5</sub> to PF<sub>7</sub>)

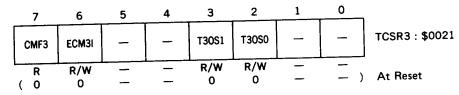

$RS_0$  to  $RS_3$  inputs are used to select either the Parallel Communication Control and Status Register (\$002B) or one of the parallel communication data registers (PCDR0: \$002C ~ PCDR14: \$003A).

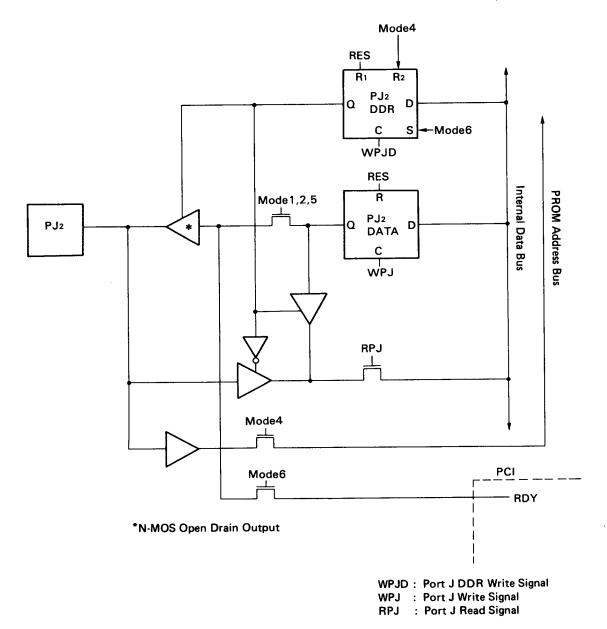

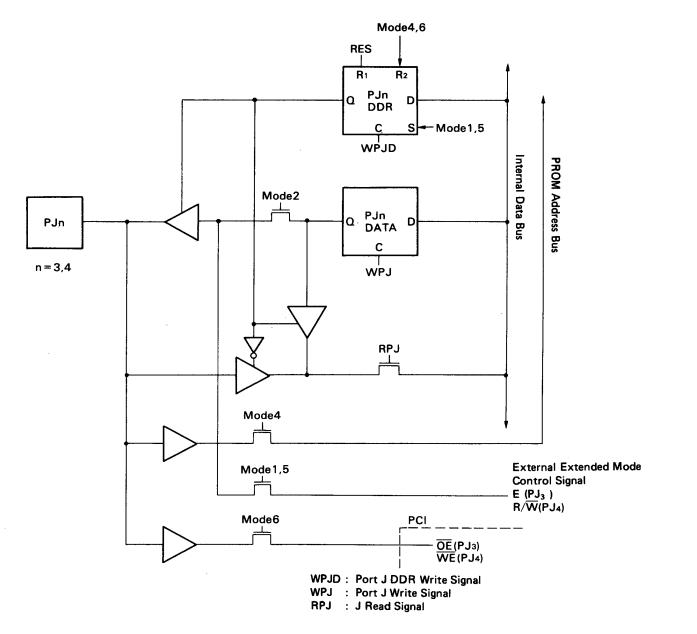

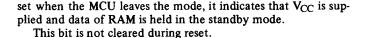

#### Ready (RDY: PJ<sub>2</sub>)

The  $\overline{RDY}$  output applies an interrupt to the master MCU when it is pulled low.

#### Output Enable (OE : PJ<sub>3</sub>)

When a logic low is applied to the  $\overline{OE}$  pin, the HD63705Z0 MCU outputs data on the master MCU data bus lines.

#### • Write Enable (WE : PJ<sub>4</sub>)

When a logic low is applied to the  $\overline{WE}$  pin, the master MCU writes data to the HD63705Z0 MCU via data bus lines.

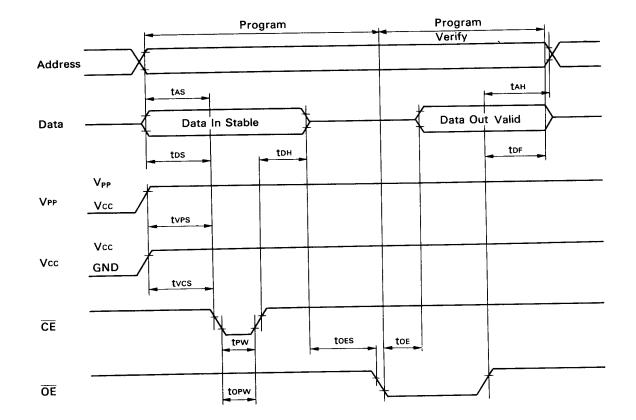

#### PROM Programming Mode Pins

The following pins are used in the **PROM** programming mode (Mode 4).

#### Chip Enable (CE : PA<sub>0</sub>)

When a logic low is applied to the  $\overline{CE}$  pin, the HD63705Z0 PROM is enabled to be programmed and verified. A high level on this pin disallows PROM programming and verification.

#### Output Enable (OE: PA1)

This input pin controls the PROM data output. A low level on the  $\overrightarrow{OE}$  pin enables programmed PROM data to be output.

• Programming Voltage (V<sub>PP</sub> : MP<sub>2</sub>)

The PROM can be programmed while the programming

voltage is applied to this V<sub>PP</sub> pin. The PROM address is input via NMI, Port F, Port H and Port J (EA<sub>0</sub> to EA<sub>14</sub>). The programmed PROM data is output from Port C (EO<sub>0</sub> to EO<sub>7</sub>). For details, see 'PROGRAMMING THE PROM'.

#### I/O Ports

The HD63705Z0 provides nine I/O ports: seven 8-bit ports, a 7-bit port and a 5-bit port.

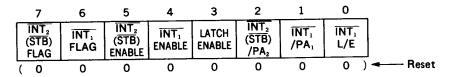

#### • Port A ( $PA_0$ to $PA_6$ )

This is a 7-bit output only port. Of the seven output lines, three lines can be used also for other purposes.

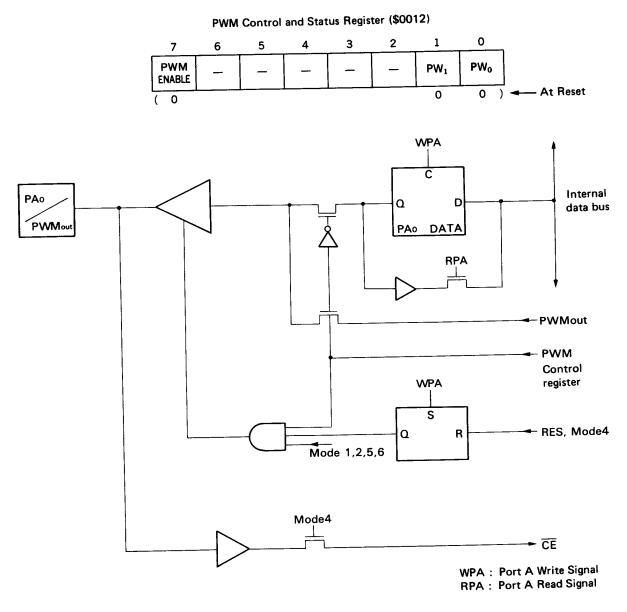

Port A bit 0 (PA<sub>0</sub>) can also be utilized as the output of PWM timer. It functions as  $\overline{CE}$  input pin in the PROM programming mode (Mode 4).

$PA_1$  can also be used for  $\overline{INT_1}$  input. It is configured as  $\overline{OE}$  input in the PROM programming mode (Mode 4).

$PA_2$  can be also used for  $\overline{INT_2}$  (STB) input.

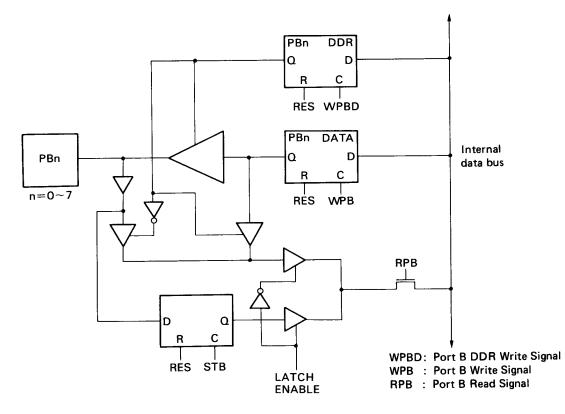

#### Port B (PB<sub>0</sub> to PB<sub>7</sub>)

This is an 8-bit I/O port. It can also be used as an input data latch port.

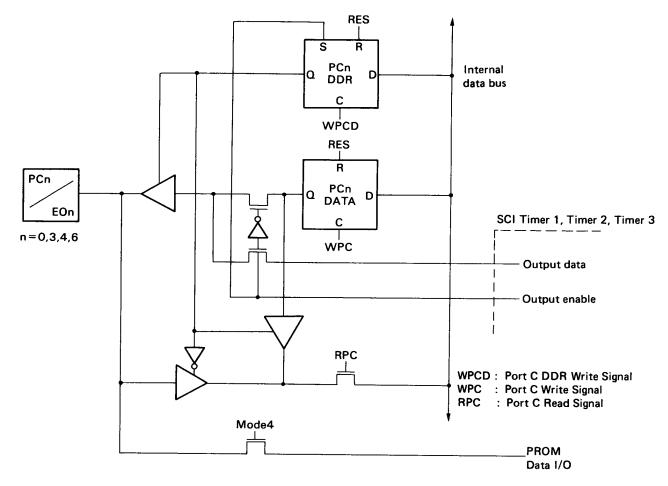

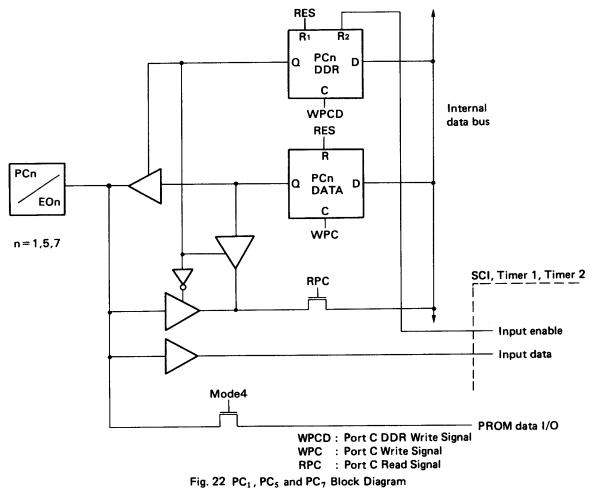

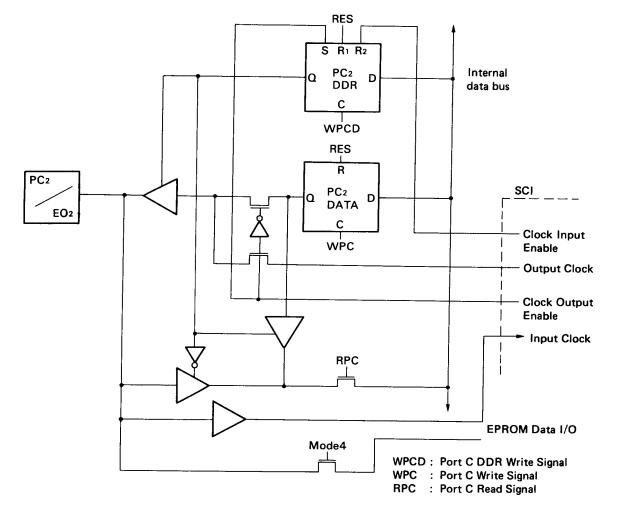

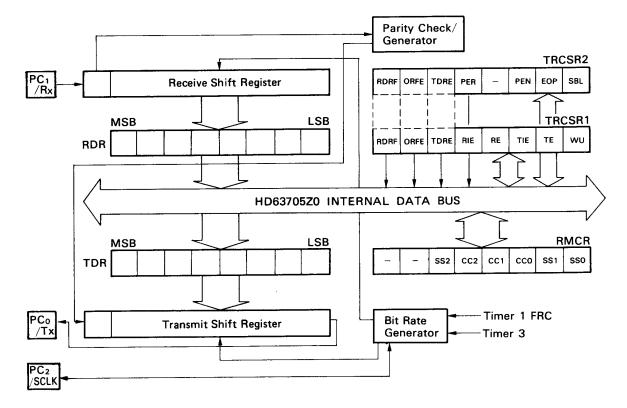

#### • Port C (PC<sub>0</sub> to PC<sub>7</sub>)

This is an 8-bit I/O port.  $PC_0$  to  $PC_2$  can also be used as SCI I/O lines.  $PC_3$  to  $PC_7$  can also function as I/O pins of Timer 1, Timer 2 and Timer 3. In the PROM programming mode (Mode 4) Port C provides bidirectional PROM data lines (EO<sub>0</sub> to EO<sub>7</sub>).

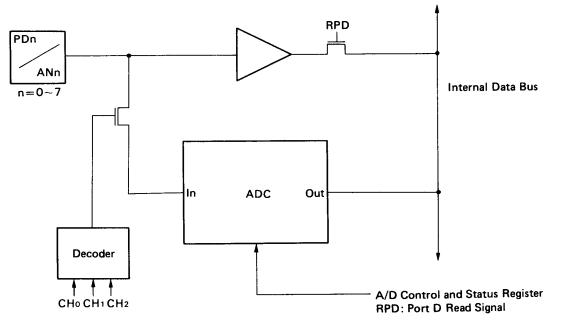

#### Port D (PD<sub>0</sub> to PD<sub>7</sub>)

This is an 8-bit input only port. It can also provide A/D channel input lines (AN<sub>0</sub> to AN<sub>7</sub>).

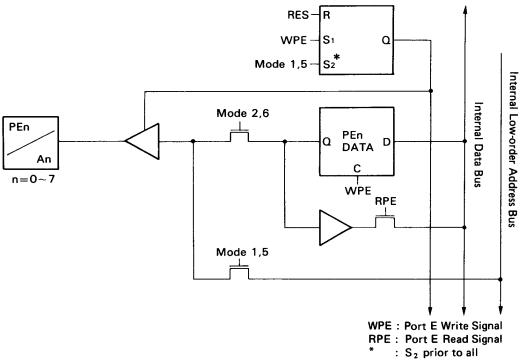

#### Port E (PE<sub>0</sub> to PE<sub>7</sub>)

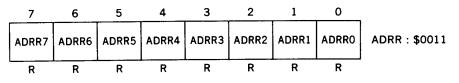

This is an 8-bit output only port. It is a high-current drive port which produces 10 mA as  $I_{OL}$  when  $V_{OL} = 1.0V$ . In the external extended modes (Mode 1 and Mode 5) Port E provides the eight low-order address bus output lines (ADR<sub>0</sub> to ADR<sub>7</sub>).

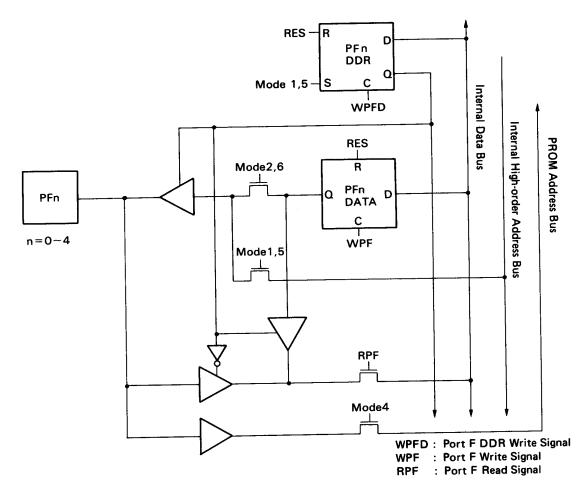

#### • Port F (PF<sub>0</sub> to PF<sub>7</sub>)

This is an 8-bit I/O port. In the external extended modes (Mode 1 and Mode 5) Port F provides the eight high-order address output lines (ADR<sub>8</sub> to ADR<sub>15</sub>). In the slave MCU mode (Mode 6), PF<sub>5</sub> to PF<sub>7</sub> function as register select pins (RS<sub>1</sub> to RS<sub>3</sub>). In the PROM programming mode (Mode 4). Port F provides PROM address input lines (EA<sub>4</sub>, EA<sub>7</sub>, EA<sub>8</sub>, EA<sub>10</sub> to EA<sub>14</sub>).

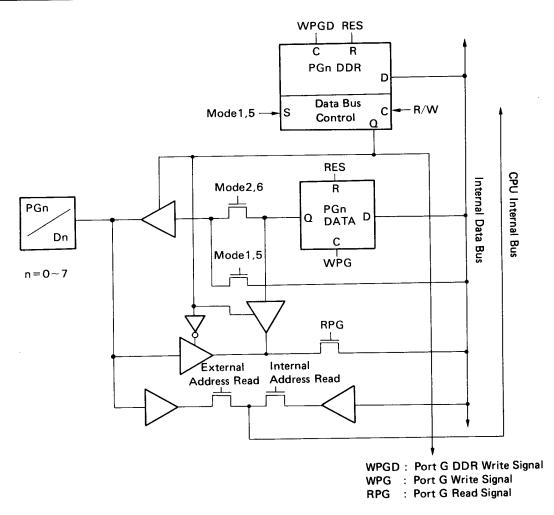

#### • Port G ( $PG_0$ to $PG_7$ )

This is an 8-bit I/O port. In the external extended modes (Mode 1 and Mode 5) Port G provides eight data lines (DATA<sub>0</sub> to DATA<sub>7</sub>).

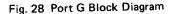

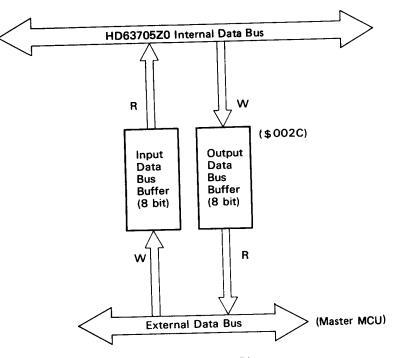

• Port H (PH<sub>0</sub> to PH<sub>7</sub>) This is an 8-bit I/O port. In the slave MCU mode (Mode 6), Port H functions as 8-bit bidirectional data bus between the HD63705Z0 MCU and the master MCU (DBB<sub>0</sub> to DBB<sub>7</sub>).

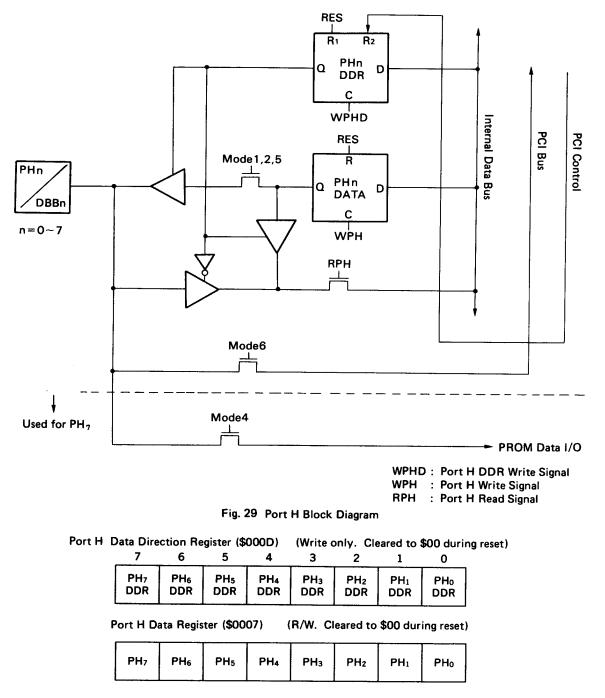

#### • Port J (PJ<sub>0</sub> to PJ<sub>4</sub>)

This is a 5-bit I/O port. In the master MCU external extended modes (Mode 1 and Mode 5),  $PJ_3$  and  $PJ_4$  function as E and  $R/\overline{W}$  outputs respectively. In the slave MCU mode (Mode 6),  $PJ_0$ ,  $PJ_1$ ,  $PJ_2$ ,  $PJ_3$  and  $PJ_4$  are used as  $\overline{CS}$  input,  $RS_0$  input,  $\overline{RDY}$  output,  $\overline{OE}$  input and  $\overline{WE}$  input respectively. In the PROM programming mode (Mode 4), Port J provides PROM address input lines (EA<sub>0</sub> to EA<sub>3</sub>, EA<sub>6</sub>).

For detailed information about these ports, see 'I/O PORT'.

#### MODE SELECTION

The HD63705ZO is capable of operating in five modes; four MCU modes and a PROM mode. The following is a description of individual modes.

#### MCU Modes

#### Mode 1 (Master MCU External Extended Mode)

In this mode Port G provides data lines, Port E provides the eight low-order address bus lines, and Port F provides the eight high-order address bus lines. The HD63705Z0 provides direct interface with the HMCS6800 via these lines. To control the interface,  $R/\overline{W}$  and E signals are output from  $PJ_4$  and  $PJ_3$  respectively. In this mode, the internal PROM is enabled which allows the MCU to address up to 56k bytes external memory space.

#### Mode 2 (Master MCU Single Chip Mode)

In this mode all of the nine ports can be used.

#### Mode 5 (Master MCU External Extended Mode)

This mode is, like Mode 1, an external extended mode. In this mode, however, the internal PROM is disabled which allows the MCU to address up to 65k byte external memory space.

#### Mode 6 (Slave MCU Single Chip Mode)

In this mode the HD63705Z0 functions as an intelligent peripheral interface adapter LSI. The device provides a parallel communication interface with the master MCU via Port H. Port F and Port J are used to select a parallel communication register and control the parallel communication. The internal PROM is enabled which disallows the MCU to address external memory space. This mode provides 52 available port lines (all lines of Port A, B, C, D, E, G and PF<sub>0</sub> to PF<sub>4</sub>).

#### PROM Programming Mode (Mode 4)

This mode allows the PROM to be programmed. For details see 'PROGRAMMING THE PROM'.

Table 6 and Fig. 12 shows MCU port condition in each mode and memory map in each mode respectively.

#### PIN FUNCTION SUMMARY

The condition of the pins depends on the operating mode.

For detail, see 'FUNCTIONAL PIN DESCRIPTION'.

#### **Table 1 Pin Function Summary**

| No. | Mode 1, 5                                      | Mode 2        | Mode 6                 | Mode 4                                 |

|-----|------------------------------------------------|---------------|------------------------|----------------------------------------|

| 1   | Port B <sub>6</sub> (I/O)                      | +             | ÷                      |                                        |

| 2   | Port B <sub>7</sub> (I/O)                      | <del>~</del>  | <del>~</del>           |                                        |

| 3   | RES                                            | <del>~</del>  | ← ·                    |                                        |

| 4   | XTAL                                           | <del>~</del>  | ÷                      |                                        |

| 5   | EXTAL                                          | ←             | ÷                      |                                        |

| 6   | MP <sub>1</sub> (I)                            | <del>~</del>  | +                      | <del>~</del>                           |

| 7   | MP <sub>0</sub> (1)                            | <del>~</del>  | <del>&lt;-</del>       | *                                      |

| 8   | NMI                                            | <del>~-</del> | +                      | EA, (I)                                |

| 9   | STBY                                           | ÷             | ÷                      | +                                      |

| 10  | V <sub>cc</sub>                                | ÷             | ÷                      | ÷                                      |

| 11  | Port C <sub>7</sub> (I/O)/Tin <sub>1</sub>     | ÷-            |                        | EO7 (I/O)                              |

| 12  | Port C <sub>6</sub> (I/O)Tout <sub>1</sub>     | <del>~</del>  | ÷                      | EO <sub>6</sub> (I/O)                  |

| 13  | Port C <sub>5</sub> (I/O)/Tin <sub>2</sub>     | <del>~</del>  | +                      | EO <sub>5</sub> (I/O)                  |

| 14  | Port C <sub>4</sub> (I/O)/Tout <sub>2</sub>    | ÷             | ÷                      | EO4 (1/O)                              |

| 15  | Port C <sub>3</sub> (I/O)/Tout <sub>3</sub>    | ÷             | ÷                      | EO <sub>3</sub> (I/O)                  |

| 16  | Port C <sub>2</sub> (I/O)/SCLK                 | ÷             | ÷                      | EO <sub>2</sub> (I/O)                  |

| 17  | Port C <sub>1</sub> (I/O)/Rx                   |               | ÷                      | EO <sub>1</sub> (I/O)                  |

| 18  | Port C <sub>0</sub> (I/O)/Tx                   | <del>~</del>  | ÷                      | EO <sub>0</sub> (I/O)                  |

| 19  | Port A <sub>0</sub> (O)/PWMout                 | ←             | ÷                      | CE (I)                                 |

| 20  | Port A <sub>1</sub> (O)/ $\overline{INT_1}$    | ÷             | ÷                      | OE (I)                                 |

| 21  | Port A <sub>2</sub> (O)/INT <sub>2</sub> (STB) | <del>~</del>  | ÷                      | ·                                      |

| 22  | Port A <sub>3</sub> (O)                        | ÷             | <i>←</i>               |                                        |

| 23  | Port A <sub>4</sub> (O)                        | +             | ←                      |                                        |

| 24  | Port A <sub>5</sub> (O)                        | <del>~</del>  | <b>←</b>               |                                        |

| 25  | Port A <sub>6</sub> (O)                        | ←             | <i>←</i>               |                                        |

| 26  | AV <sub>CC</sub>                               | ←             | ←                      |                                        |

| 27  | Port D <sub>0</sub> (I)/AN <sub>0</sub>        | ←             | ←                      |                                        |

| 28  | Port $D_1$ (I)/AN <sub>1</sub>                 | +             | <i>←</i>               |                                        |

| 29  | Port D <sub>2</sub> (I)/AN <sub>2</sub>        | ←             | <del>~</del>           |                                        |

| 30  | Port D <sub>3</sub> (I)/AN <sub>3</sub>        | ←             | +                      |                                        |

| 31  | Port D <sub>4</sub> (I)/AN <sub>4</sub>        | ←             | +                      |                                        |

| 32  | Port D <sub>5</sub> (I)/AN <sub>5</sub>        | <u>←</u>      | <del>~</del>           |                                        |

| 33  | Port $D_6$ (I)/AN <sub>6</sub>                 | <del>~</del>  | +                      | · · · · · · · · · · · · · · · · · · ·  |

| 34  | Port D <sub>7</sub> (I)/AN <sub>7</sub>        | <u>←</u> `    | +                      |                                        |

| 35  | AV <sub>SS</sub>                               | ÷             | +                      |                                        |

| 36  | Port H <sub>o</sub> (I/O)                      | ÷             | DBB <sub>0</sub> (I/O) | 1788                                   |

| 37  | Port H <sub>1</sub> (I/O)                      | ÷             | DBB <sub>1</sub> (I/O) |                                        |

| 38  | Port H <sub>2</sub> (I/O)                      | ÷             | DBB <sub>2</sub> (I/O) |                                        |

| 39  | Port H <sub>3</sub> (I/O)                      | ÷             | DBB <sub>3</sub> (I/O) | ······································ |

| 40  | Port H <sub>4</sub> (I/O)                      | <del>~</del>  | DBB <sub>4</sub> (I/O) |                                        |

(To be continued)

| No. | Mode 1, 5                 | Mode 2                    | Mode 6                    | Mode 4                                 |

|-----|---------------------------|---------------------------|---------------------------|----------------------------------------|

| 41  | Port H <sub>5</sub> (I/O) | ÷                         | DBB <sub>5</sub> (I/O)    |                                        |

| 42  | Port H <sub>6</sub> (I/O) | ÷                         | DBB <sub>6</sub> (I/O)    | ······································ |

| 43  | Port H <sub>7</sub> (I/O) | ÷                         | DBB <sub>7</sub> (I/O)    | EA <sub>5</sub> (I)                    |

| 44  | R/W (O)                   | Port J <sub>4</sub> (I/O) | WE (I)                    | EA <sub>6</sub> (I)                    |

| 45  | E (O)                     | Port J <sub>3</sub> (1/O) | ŌĒ (I)                    | EA <sub>0</sub> (I)                    |

| 46  | Port J <sub>2</sub> (I/O) | ÷                         | RDY (O)                   | EA <sub>1</sub> (I)                    |

| 47  | Port J <sub>1</sub> (I/O) | ÷                         | RS <sub>0</sub> (I)       | $EA_2$ (I)                             |

| 48  | Port J <sub>0</sub> (1/O) | ÷                         | <u>CS</u> (I)             | EA3 (I)                                |

| 49  | ADR <sub>15</sub> (O)     | Port $F_7$ (I/O)          | RS <sub>3</sub> (I)       | EA4 (I)                                |

| 50  | ADR <sub>14</sub> (O)     | Port F <sub>6</sub> (I/O) | RS <sub>2</sub> (I)       | EA <sub>14</sub> (I)                   |

| 51  | ADR <sub>13</sub> (O)     | Port F <sub>5</sub> (I/O) | RS <sub>1</sub> (I)       | EA <sub>13</sub> (I)                   |

| 52  | ADR <sub>12</sub> (O)     | Port F <sub>4</sub> (I/O) | Port F <sub>4</sub> (I/O) | EA <sub>12</sub> (I)                   |

| 53  | ADR <sub>11</sub> (O)     | Port F <sub>3</sub> (I/O) | Port F <sub>3</sub> (I/O) | EA <sub>11</sub> (I)                   |

| 54  | ADR <sub>10</sub> (O)     | Port F <sub>2</sub> (I/O) | Port F <sub>2</sub> (1/O) | EA10 (I)                               |

| 55  | ADR <sub>9</sub> (O)      | Port $F_1$ (I/O)          | Port $F_1$ (I/O)          | EA <sub>7</sub> (I)                    |

| 56  | ADR <sub>8</sub> (O)      | Port F <sub>0</sub> (I/O) | Port $F_0$ (I/O)          | EA <sub>8</sub> (I)                    |

| 57  | MP <sub>2</sub>           | ÷                         | ÷                         | VPP                                    |

| 58  | V <sub>SS</sub>           | ←                         | +                         | ~                                      |

| 59  | ADR <sub>7</sub> (O)      | Port E <sub>7</sub> (O)   | Port E <sub>7</sub> (O)   |                                        |

| 60  | ADR <sub>6</sub> (O)      | Port E <sub>6</sub> (O)   | Port E <sub>6</sub> (O)   |                                        |

| 61  | ADR <sub>5</sub> (0)      | Port $E_5$ (O)            | Port E <sub>5</sub> (O)   |                                        |

| 62  | ADR4 (0)                  | Port E <sub>4</sub> (O)   | Port E <sub>4</sub> (O)   |                                        |

| 63  | ADR <sub>3</sub> (O)      | Port $E_3$ (O)            | Port E <sub>3</sub> (O)   |                                        |

| 64  | $ADR_2$ (O)               | Port E <sub>2</sub> (O)   | Port E <sub>2</sub> (O)   |                                        |

| 65  | ADR1 (0)                  | Port E <sub>1</sub> (O)   | Port E <sub>1</sub> (O)   |                                        |

| 66  | $ADR_0$ (O)               | Port $E_0$ (O)            | Port E <sub>0</sub> (O)   |                                        |

| 67  | DATA <sub>0</sub> (I/O)   | Port G <sub>0</sub> (I/O) | Port G <sub>0</sub> (I/O) |                                        |

| 68  | DATA <sub>1</sub> (I/O)   | Port G <sub>1</sub> (I/O) | Port G <sub>1</sub> (I/O) |                                        |

| 69  | DATA <sub>2</sub> (I/O)   | Port G <sub>2</sub> (I/O) | Port G <sub>2</sub> (I/O) |                                        |

| 70  | DATA <sub>3</sub> (1/0)   | Port G <sub>3</sub> (I/O) | Port G <sub>3</sub> (I/O) |                                        |

| 71  | DATA <sub>4</sub> (I/O)   | Port G <sub>4</sub> (I/O) | Port G <sub>4</sub> (1/O) |                                        |

| 72  | DATA <sub>5</sub> (I/O)   | Port G <sub>5</sub> (I/O) | Port G <sub>5</sub> (I/O) |                                        |

| 73  | DATA <sub>6</sub> (I/O)   | Port G <sub>6</sub> (I/O) | Port G <sub>6</sub> (I/O) |                                        |

| 74  | DATA <sub>7</sub> (I/O)   | Port G <sub>7</sub> (I/O) | Port $G_7$ (I/O)          | ······                                 |

| 75  | Port B <sub>0</sub> (I/O) | ←                         | <del>~</del>              |                                        |

| 76  | Port B <sub>1</sub> (I/O) | ←                         | +                         |                                        |

| 77  | Port B <sub>2</sub> (I/O) | <u></u> ←                 | ÷                         |                                        |

| 78  | Port B <sub>3</sub> (I/O) | ←                         | <u> </u>                  |                                        |

| 79  | Port B <sub>4</sub> (I/O) | <u>←</u>                  | ÷                         | ·····                                  |

| 80  | Port B <sub>5</sub> (I/O) | <del>~</del>              | ÷                         |                                        |

(to be continued)

| Pin<br>No. | Main                      | Sub                          | Pin<br>No. | Main                      | Sub |

|------------|---------------------------|------------------------------|------------|---------------------------|-----|

| 1          | Port B <sub>6</sub> (I/O) |                              | 41         | Port H <sub>5</sub> (I)   |     |

| 2          | Port $B_7$ (I/O)          |                              | 42         | Port H <sub>6</sub> (I)   |     |

| 3          | RES                       |                              | 43         | Port $H_7$ (I)            |     |

| 4          | XTAL                      |                              | 44         | R/W (O)                   |     |

| 5          | EXTAL                     |                              | 45         | E (O)                     |     |

| 6          | MP1 ('L')                 |                              | 46         | Port $J_2$ (I/O)          |     |

| 7          | MP <sub>0</sub> ('H')     |                              | 47         | Port J <sub>1</sub> (I/O) |     |

| 8          | NMI                       |                              | 48         | Port J <sub>0</sub> (I/O) |     |

| 9          | STBY                      |                              | 49         | ADR <sub>15</sub> (O)     |     |

| 10         | V <sub>CC</sub>           |                              | 50         | ADR <sub>14</sub> (O)     |     |

| 11         | Port $C_7$ (I/O)          | Tin1 (I)                     | 51         | ADR <sub>13</sub> (O)     |     |

| 12         | Port $C_6$ (I/O)          | Touti (O)                    | 52         | ADR <sub>12</sub> (O)     |     |

| 13         | Port C <sub>5</sub> (I/O) | Tin <sub>2</sub> (1)         | 53         | ADR <sub>11</sub> (O)     |     |

| 14         | Port C <sub>4</sub> (1/O) | Tout <sub>2</sub> (O)        | 54         | ADR <sub>10</sub> (O)     |     |

| 15         | Port $C_3$ (I/O)          | Touts (O)                    | 55         | ADR, (O)                  |     |

| 16         | Port $C_2$ (I/O)          | SCLK (I/O)                   | 56         | ADR <sub>8</sub> (O)      |     |

| 17         | Port $C_1$ (I/O)          | Rx (I)                       | 57         | MP <sub>2</sub> ('L/H')   |     |

| 18         | Port $C_0$ (I/O)          | Tx (O)                       | 58         | V <sub>SS</sub>           |     |

| 19         | Port $A_0$ (O)            | PWMout (O)                   | 59         | ADR <sub>7</sub> (O)      |     |

| 20         | Port A <sub>1</sub> (O)   | $\overline{INT_1}$ (I)       | 60         | ADR <sub>6</sub> (O)      |     |

| 21         | Port A <sub>2</sub> (O)   | $\overline{INT_2}$ (STB) (1) | 61         | ADR <sub>5</sub> (O)      |     |

| 22         | Port $A_3$ (O)            |                              | 62         | ADR4 (0)                  |     |

| 23         | Port A <sub>4</sub> (O)   |                              | 63         | ADR <sub>3</sub> (O)      |     |

| 24         | Port $A_5$ (O)            |                              | 64         | ADR <sub>2</sub> (O)      |     |

| 25         | Port $A_6$ (O)            |                              | 65         | ADR <sub>1</sub> (O)      |     |

| 26         | AV <sub>CC</sub>          |                              | 66         | $ADR_0$ (O)               |     |

| 27         | Port $D_0$ (I)            | AN <sub>0</sub> (I)          | 67         | DATA <sub>0</sub> (I/O)   |     |

| 28         | Port D <sub>1</sub> (I)   | AN <sub>1</sub> (I)          | 68         | DATA <sub>1</sub> (I/O)   |     |

| 29         | Port $D_2$ (I)            | AN <sub>2</sub> (I)          | 69         | DATA <sub>2</sub> (I/O)   |     |

| 30         | Port D <sub>3</sub> (I)   | AN <sub>3</sub> (I)          | 70         | DATA <sub>3</sub> (I/O)   |     |

| 31         | Port D <sub>4</sub> (I)   | AN <sub>4</sub> (I)          | 71         | DATA4 (1/O)               |     |

| 32         | Port D <sub>5</sub> (I)   | AN <sub>5</sub> (I)          | 72         | DATA <sub>s</sub> (I/O)   |     |

| 33         | Port $D_6$ (I)            | AN <sub>6</sub> (I)          | 73         | DATA <sub>6</sub> (I/O)   |     |

| 34         | Port $D_7$ (I)            | AN <sub>7</sub> (I)          | 74         | DATA <sub>7</sub> (I/O)   | 1   |

| 35         | AV <sub>SS</sub>          |                              | 75         | Port B <sub>0</sub> (I/O) |     |

| 36         | Port $H_0$ (I/O)          |                              | 76         | Port $B_1$ (I/O)          |     |

| 37         | Port H <sub>1</sub> (I/O) |                              | 77         | Port $B_2$ (I/O)          |     |

| 38         | Port $H_2$ (I/O)          |                              | 78         | Port $B_3$ (I/O)          |     |

| 39         | Port H <sub>3</sub> (I/O) |                              | 79         | Port B <sub>4</sub> (I/O) |     |

| 40         | Port H <sub>4</sub> (I/O) |                              | 80         | Port B <sub>5</sub> (I/O) |     |

Internal ROM is enabled in Mode 1. Internal ROM is disabled in Mode 5.

**OHITACHI**

| Pin<br>No. | Main                      | Sub                          | No. | Main                      | Sub |

|------------|---------------------------|------------------------------|-----|---------------------------|-----|

| 1          | Port B <sub>6</sub> (1/O) |                              | 41  | Port H <sub>5</sub> (I/O) |     |

| 2          | Port $B_7$ (I/O)          | }                            | 42  | Port H <sub>6</sub> (I/O) |     |

| 3          | RES                       |                              | 43  | Port H <sub>7</sub> (I/O) |     |

| 4          | XTAL                      |                              | 44  | Port J <sub>4</sub> II/O) |     |

| 5          | EXTAL                     |                              | 45  | Port J <sub>3</sub> (1/O) |     |

| 6          | MP <sub>1</sub> ('H')     |                              | 46  | Port $J_2$ (I/O)          |     |

| 7          | $MP_0$ ('L')              |                              | 47  | Port $J_1$ (I/O)          |     |

| 8          | NMI                       |                              | 48  | Port $J_0$ (I/O)          |     |

| 9          | STBY                      |                              | 49  | Port $F_7$ (I/O)          |     |

| 10         | V <sub>CC</sub>           |                              | 50  | Port F <sub>6</sub> (I/O) |     |

| 11         | Port C <sub>7</sub> (1/O) | Tini (I)                     | 51  | Port $F_5$ (I/O)          |     |

| 12         | Port $C_6$ (I/O)          | Touti (O)                    | 52  | Port F <sub>4</sub> (I/O) |     |

| 13         | Port C <sub>5</sub> (1/O) | Tin2 (1)                     | 53  | Port $F_3$ (I/O)          |     |

| 14         | Port C <sub>4</sub> (I/O) | Tout <sub>2</sub> (O)        | 54  | Port $F_2$ (1/O)          |     |

| 15         | Port C <sub>3</sub> (I/O) | Touts (O)                    | 55  | Port $F_1$ (I/O)          |     |

| 16         | Port $C_2$ (I/O)          | SCLK (1/O)                   | 56  | Port F <sub>0</sub> (I/O) |     |

| 17         | Port $C_1$ (I/O)          | Rx (I)                       | 57  | MP <sub>2</sub> ('L')     |     |

| 18         | Port $C_0$ (I/O)          | Tx (O)                       | 58  | V <sub>SS</sub>           |     |

| 19         | Port $A_0$ (O)            | PWMout (O)                   | 59  | Port $E_7$ (O)            |     |

| 20         | Port A <sub>1</sub> (O)   | $\overline{INT_1}$ (I)       | 60  | Port E <sub>6</sub> (O)   |     |

| 21         | Port $A_2$ (O)            | $\overline{INT_2}$ (STB) (I) | 61  | Port E <sub>5.</sub> (O)  |     |

| 22         | Port $A_3$ (O)            |                              | 62  | Port E <sub>4</sub> (O)   |     |

| 23         | Port A <sub>4</sub> (O)   |                              | 63  | Port E <sub>3</sub> (O)   |     |

| 24         | Port A <sub>5</sub> (O)   |                              | 64  | Port $E_2$ (O)            |     |

| 25         | Port $A_6$ (O)            |                              | 65  | Port $E_1$ (O)            |     |

| 26         | AV <sub>CC</sub>          |                              | 66  | Port $E_0$ (O)            |     |

| 27         | Port $D_0$ (I)            | $AN_0$ (I)                   | 67  | Port $G_0$ (I/O)          |     |

| 28         | Port $D_1$ (I)            | AN <sub>1</sub> (I)          | 68  | Port $G_1$ (I/O)          |     |

| 29         | Port $D_2$ (I)            | AN <sub>2</sub> (1)          | 69  | Port $G_2$ (1/O)          |     |

| 30         | Port $D_3$ (I)            | AN <sub>3</sub> (I)          | 70  | Port $G_3$ (I/O)          |     |

| 31         | Port D <sub>4</sub> (I)   | AN4 (I)                      | 71  | Port $G_4$ (I/O)          |     |

| 32         | Port D <sub>5</sub> (I)   | AN <sub>5</sub> (I)          | 72  | Port $G_5$ (1/O)          |     |

| 33         | Port D <sub>6</sub> (I)   | AN <sub>6</sub> (I)          | 73  | Port $G_6$ (I/O)          |     |

| 34         | Port $D_7$ (I)            | AN <sub>7</sub> (I)          | 74  | Port $G_7$ (I/O)          |     |

| 35         | AV <sub>SS</sub>          |                              | 75  | Port $B_0$ (I/O)          |     |

| 36         | Port $H_0$ (1/O)          |                              | 76  | Port B <sub>1</sub> (I/O) |     |

| 37         | Port H <sub>1</sub> (I/O) |                              | 77  | Port B <sub>2</sub> (I/O) |     |

| 38         | Port $H_2$ (I/O)          |                              | 78  | Port $B_3$ (I/O)          |     |

| 39         | Port H <sub>3</sub> (I/O) |                              | 79  | Port $B_4$ (I/O)          |     |

| 40         | Port H <sub>4</sub> (I/O) |                              | 80  | Port B <sub>5</sub> (I/O) |     |

### Table 3 Pin Function in Master MCU Single Chip Mode (Mode 2)

This Material Copyrighted By Its Respective Manufacturer

| Table 4 | Pin | Function | in Slave | <b>MCU Single</b> | Chip | Mode ( | Mode 6) |

|---------|-----|----------|----------|-------------------|------|--------|---------|

|---------|-----|----------|----------|-------------------|------|--------|---------|

| Pin<br>No. | Main                      | Sub                                   | Pin<br>No. | Main                      | Sub |

|------------|---------------------------|---------------------------------------|------------|---------------------------|-----|

| 1          | Port B <sub>6</sub> (I/O) |                                       | 41         | DBB <sub>5</sub> (I/O)    |     |

| 2          | Port $B_7$ (I/O)          |                                       | 42         | DBB <sub>6</sub> (1/O)    |     |

| 3          | RES                       |                                       | 43         | DBB7 (I/O)                |     |

| 4          | XTAL                      |                                       | 44         | WE (I)                    |     |

| 5          | EXTAL                     |                                       | 45         | OE (I)                    |     |

| 6          | MP1 ('H')                 |                                       | 46         | RDY (O)                   |     |

| 7          | MP <sub>0</sub> ('L')     |                                       | 47         | RS <sub>0</sub> (I)       |     |

| 8          | NMI                       |                                       | 48         | <u>CS</u> (I)             |     |

| 9          | STBY                      |                                       | 49         | RS <sub>3</sub> (I)       |     |

| 10         | V <sub>CC</sub>           |                                       | 50         | RS <sub>2</sub> (I)       |     |

| 11         | Port $C_7$ (I/O)          | Tin1 (I)                              | 51         | RS <sub>1</sub> (I)       |     |

| 12         | Port C <sub>6</sub> (I/O) | Touti (O)                             | 52         | Port $F_4$ (I/O)          |     |

| 13         | Port C <sub>5</sub> (I/O) | Tin2 (1)                              | 53         | Port $F_3$ (I/O)          |     |

| 14         | Port C <sub>4</sub> (I/O) | Tout2 (O)                             | 54         | Port $F_2$ (I/O)          |     |

| 15         | Port C <sub>3</sub> (I/O) | Touts (O)                             | 55         | Port $F_1$ (I/O)          |     |

| 16         | Port C <sub>2</sub> (I/O) | SCLK (1/O)                            | 56         | Port $F_0$ (I/O)          |     |

| 17         | Port $C_1$ (I/O)          | Rx (I)                                | 57         | MP <sub>2</sub> ('H')     |     |

| 18         | Port $C_0$ (I/O)          | Tx (O)                                | 58         | V <sub>SS</sub>           |     |

| 19         | Port $A_0$ (O)            | PWMout (O)                            | 59         | Port $E_7$ (O)            |     |

| 20         | Port $A_1$ (O)            | $\overline{INT_1}$ (I)                | 60         | Port $E_6$ (O)            |     |

| 21         | Port $A_2$ (O)            | $\overline{\mathrm{INT}_2}$ (STB) (1) | 61         | Port $E_5$ (O)            |     |

| 22         | Port $A_3$ (O)            |                                       | 62         | Port E <sub>4</sub> (O)   |     |

| 23         | Port A <sub>4</sub> (O)   |                                       | 63         | Port E <sub>3</sub> (O)   |     |

| 24         | Port $A_5$ (O)            |                                       | 64         | Port E <sub>2</sub> (O)   |     |

| 25         | Port $A_6$ (O)            |                                       | 65         | Port E <sub>1</sub> (O)   |     |

| 26         | AV <sub>CC</sub>          |                                       | 66         | Port $E_0$ (O)            |     |

| 27         | Port $D_0$ (I)            | AN <sub>0</sub> (I)                   | 67         | Port $G_0$ (I/O)          | ſ   |

| 28         | Port $D_1$ (I)            | AN1 (I)                               | 68         | Port $G_1$ (I/O)          |     |

| 29         | Port $D_2$ (I)            | AN <sub>2</sub> (I)                   | 69         | Port $G_2$ (I/O)          |     |

| 30         | Port $D_3$ (I)            | AN <sub>3</sub> (I)                   | 70         | Port $G_3$ (I/O)          |     |

| 31         | Port D <sub>4</sub> (I)   | AN4 (I)                               | 71         | Port G <sub>4</sub> (I/O) |     |

| 32         | Port $D_5$ (I)            | AN <sub>5</sub> (1)                   | 72         | Port G <sub>5</sub> (I/O) |     |

| 33         | Port $D_6$ (I)            | AN <sub>6</sub> (I)                   | 73         | Port G <sub>6</sub> (I/O) |     |

| 34         | Port $D_7$ (I)            | AN <sub>7</sub> (I)                   | 74         | Port G <sub>7</sub> (I/O) |     |

| 35         | AV <sub>SS</sub>          |                                       | 75         | Port $B_0$ (I/O)          |     |

| 36         | DBB <sub>0</sub> (I/O)    |                                       | 76         | Port B <sub>1</sub> (I/O) |     |

| 37         | DBB <sub>1</sub> (I/O)    |                                       | 77         | Port B <sub>2</sub> (I/O) |     |

| 38         | DBB <sub>2</sub> (I/O)    |                                       | 78         | Port B <sub>3</sub> (I/O) |     |

| 39         | DBB <sub>3</sub> (I/O)    |                                       | 79         | Port B <sub>4</sub> (I/O) |     |

| 40         | DBB <sub>4</sub> (I/O)    |                                       | 80         | Port B <sub>5</sub> (I/O) |     |

| Pin<br>No. | Main                     | Sub* | Pin<br>No. | Main                               | Sub* |

|------------|--------------------------|------|------------|------------------------------------|------|

| 1          | (Not Used)               |      | 41         | (Not Used)                         |      |

| 2          | (Not Used)               |      | 42         | (Not Used)                         |      |

| 3          | (Not Used)               |      | 43         | EA₅                                | (5)  |

| 4          | (Not Used)               |      | 44         | EA <sub>6</sub>                    | (4)  |

| 5          | (Not Used)               |      | 45         | EA <sub>0</sub>                    | (10) |

| 6          | MP <sub>1</sub> ('L')    |      | 46         | EA <sub>1</sub>                    | (9)  |

| 7          | MP <sub>0</sub> ('L')    |      | 47         | EA <sub>2</sub>                    | (8)  |

| 8          | EA,                      | (24) | 48         | EA <sub>3</sub>                    | (7)  |

| 9          | STBY ('L')               |      | 49         | EA4                                | (6)  |

| 10         | V <sub>CC</sub>          | (28) | 50         | EA <sub>14</sub>                   | (27) |

| 11         | EO7                      | (19) | 51         | EA <sub>13</sub>                   | (26) |

| 12         | EO6                      | (18) | 52         | EA <sub>12</sub>                   | (2)  |

| 13         | EO₅                      | (17) | 53         | EA <sub>11</sub>                   | (23) |

| 14         | EO4                      | (16) | 54         | EA <sub>10</sub>                   | (21) |

| 15         | EO3                      | (15) | 55         | EA7                                | (3)  |

| 16         | EO <sub>2</sub>          | (13) | 56         | EA <sub>8</sub>                    | (25) |

| 17         | EO1                      | (12) | 57         | V <sub>PP</sub> (MP <sub>2</sub> ) | (1)  |

| 18         | EOo                      | (11) | 58         | V <sub>SS</sub>                    | (14) |

| 19         | CE                       | (20) | 59         | (Not Used)                         |      |

| 20         | ŌĒ                       | (22) | 60         | (Not Used)                         |      |

| 21         | (Not Used)               |      | 61         | (Not Used)                         |      |

| 22         | (Not Used)               |      | 62         | (Not Used)                         |      |

| 23         | (Not Used)               |      | 63         | (Not Used)                         |      |

| 24         | (Not Used)               |      | 64         | (Not Used)                         |      |

| 25         | (Not Used)               |      | 65         | (Not Used)<br>(Not Used)           |      |

| 26         | (Not Used)               |      | 66         | (Not Used)                         |      |

| 27         | (Not Used)               |      | 67         | (Not Used)                         |      |

| 28         | (Not Used)               |      | 68         | (Not Used)                         |      |

| 29         | (Not Used)               |      | 69         | (Not Used)                         |      |

| 30         | (Not Used)               |      | 70         | (Not Used)                         |      |

| 31         | (Not Used)               |      | 71         | (Not Used)                         |      |

| 32         | (Not Used)               |      | 72<br>73   | (Not Used)                         |      |

| 33         | (Not Used)               |      | 73         | (Not Used)                         |      |

| 34         | (Not Used)               |      | 74         | (Not Used)                         |      |

| 35         | (Not Used)               |      | 76         | (Not Used)                         |      |

| 36         | (Not Used)<br>(Not Used) |      | 77         | (Not Used)                         |      |

| 37         | (Not Used)<br>(Not Used) |      | 78         | (Not Used)                         |      |

| 38         |                          |      | 79         | (Not Used)                         |      |

| 39         | (Not Used)<br>(Not Used) |      | 80         | (Not Used)                         |      |

| 40         | (NOT Osed)               |      |            |                                    |      |

### Table 5 Pin Function in PROM Programming Mode (Mode 4)

\*Number within parenthesis for Sub Function indicates pin number of the HN27C256.

This Material Copyrighted By Its Respective Manufacturer

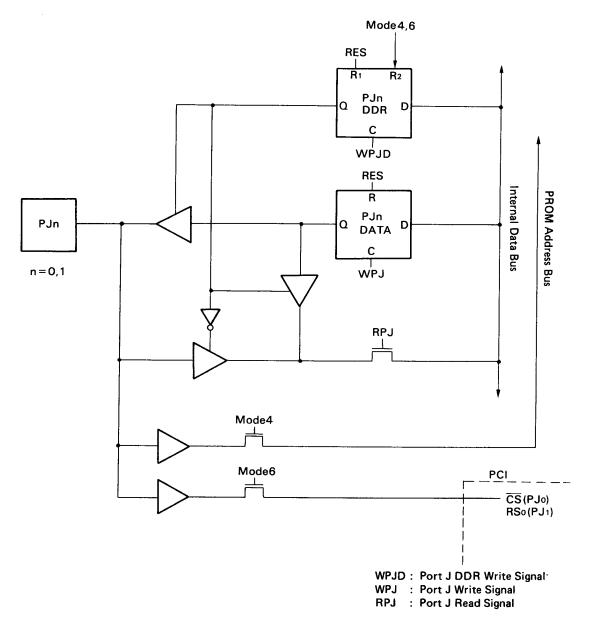

Table 6 MCU Port Condition in Each Operating Mode

| Address                                              | \$0000~<br>\$FFFF                                                                                           | \$0000~<br>\$1FFF   | \$0000~<br>\$1FFF                                                                                                   | \$0000~<br>\$FFFF                                  | \$0000~<br>\$1FFF                                                                    |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                      | \$0C                                                                                                        | \$00<br>\$1F        | \$0C<br>\$1F                                                                                                        | \$00<br>\$FF                                       | \$00<br>\$1F                                                                         |

| *2 *3<br>ROM RAM                                     | _                                                                                                           | -                   | 1                                                                                                                   | -                                                  | -                                                                                    |

| *2<br>ROM                                            | ш<br>+<br>-                                                                                                 | -                   | ۵.                                                                                                                  | ш                                                  | _                                                                                    |

| ₽J₀~PJ,*                                             | PJ <sub>5</sub> ~PJ <sub>5</sub> (I/O)<br>PJ <sub>5</sub> →E( <u>O)</u><br>PJ <sub>4</sub> →R/ <u>W</u> (O) | 0/1                 | EA3, EA3, EA1,<br>EA0, EA6 (1)                                                                                      | PJ,∽PJ,… (I/O)<br>PJ,→E ( <u>O)</u><br>PJ,→R/₩ (O) | CS, RS,, OE,<br>WE(1)<br>RDY(0)                                                      |

| РН₀∼РН₁                                              | 0/1                                                                                                         | 0/1                 | PH₀~PH₄:<br>Not Used<br>PH;→EA₅(I)                                                                                  | 0/1                                                | DBB <sub>0</sub> ~DBB, <u>CS</u> , RS <sub>6</sub> , OE,<br>(1/0) <u>RDV</u> ··· (1) |

| ₽₲~₽₲                                                | D₀~D,(1/0)                                                                                                  | 0/1                 | Not Used PH <sub>5</sub> ~PH <sub>4</sub> :<br>Not Used Not Used PH→±64,(1)                                         | D₀~D,(I/O)                                         | 0/1                                                                                  |

| ₽₣₀∼₽₣₁                                              | A <sub>6</sub> ∼A <sub>15</sub><br>(0)                                                                      | 0/1                 | EA., EA., EA.,<br>EA., EA., EA.,<br>EA., EA.(   )                                                                   | A₅~A₁₅<br>(0)                                      | PF₀~PF₄(I/O)<br>RS₁~RS₃(I)                                                           |

| PE₀~PE,                                              | A₀~A,<br>(0)                                                                                                | 0                   | Not Used                                                                                                            | A₀~A,<br>(0)                                       | 0)                                                                                   |

| PD.~PD,                                              | _                                                                                                           | ←                   | Not Used                                                                                                            | -                                                  | +                                                                                    |

| PC₀~PC,                                              | 0/1                                                                                                         | ←                   | Not Used EQ <sub>0</sub> ~EQ,(I/0) Not Used                                                                         | 0/1                                                | ←                                                                                    |

| PB₀~PB,                                              | 0/1                                                                                                         | ←                   | Not Used                                                                                                            | 0/1                                                | <b>4</b>                                                                             |

| PA₀~PA₀                                              | 1/0…PA,, PA,<br>0…PA,,PA,∼PA¢                                                                               | ←                   | PA <sub>o</sub> → <u>CE</u> (()<br>PA <sub>i</sub> → <u>PE</u> (()<br>PA <sub>i</sub> ~>PA <sub>c</sub><br>Not Used | l/0…PA,, PA₂<br>0…PA₀, PA₁~PA₅                     | <b>4</b>                                                                             |